Protocol

Bemærk: Denne protokol beskriver de procedurer, der anvendes til at fremstille, pakke og teste single-elektron pumper baseret på silicium MOS QD-teknologi. Trinene diskuteret i underafsnit 1 og 2 udføres i en ISO5 renrum, mens de i § 3 udføres i ISO6 laboratorier. Omgivelsesbetingelser løbende kontrolleres. Nominelle værdier for temperatur og fugtighed er sat til 20 ± 1 ° C og 55% ± 5% hhv.

1. mikrofabrikation

- Field Oxide

- Rengør skiven ved nedsænkning i følgende: Piranha etch (10 min), deioniseret (DI) vand (10 min), RCA-2 opløsning (DI vand 175 ml, 30 ml HCI, H 2 O 2 30 ml ved 100 ° C i 10 minutter), deioniseret vand (5 min), flussyre (HF) syre fortyndet i vand 10: 1 (10 sek), DI vand (10 min). Brug beskyttende beklædning ved håndtering HF (dvs. beskyttelsesbriller, PVC forklæde og PVC handsker). Fortsæt i den angivne rækkefølge.

- Placer waferi oxidationsovn ved 900 ° C og oxidere i trin som følger: tør O 2 (10 min), våd O 2 (40 min), tør O 2 (10 min), N2 (15 min).

- Ohmske kontakter

- Udføre fotolitografi og etch oxid.

- Deponere nogle få nm tykt lag af vedhæftningsforbedrer hexamethyldisilazan (HMDS) på waferoverfladen som følger: pre-bage på en varmeplade ved 110 ° C i 1 minut, hæld ~ 50 ml HMDS i et bægerglas, placere bægerglasset og skiven i vakuumkammeret, evakuere og vente i 2 min.

- Spinde en 2-4-um tykt lag af fotoresist på både ryg og forsider af skiven (3.000-5.000 rpm, 25-40 sek afhængigt af den ønskede tykkelse).

- Udsættes for ultraviolet lys i masken aligner (10 mW / cm2 for 4-10 sek ifølge modstå tykkelse). Post-bage på en varmeplade ved 110 ° C i 1 min.

- Udvikle til 1-2 minutter, derefter skylles i deioniseret vand. Udfør O 2 plasma etch i 20 min (tryk = 340 mTorr, indfaldende effekt = 50 W; reflekteret effekt <1 W).

- Etch oxid i pufret HF syreopløsning (15: 1, 4-5 min, ætsehastighed ≈ 20 nm / min ved 30 ° C). Skyl i deioniseret vand (5 min). Blow tørt med N2.

- Fjern fotoresist ved nedsænkning i acetone. Skyl i isopropanol (IPA), derefter blæse tør med N2.

- Placer wafer i ovn ved 1000 ° C med fosfor kilde (N2-strøm i 30-45 min afhængig af ønsket doping densitet).

- Fjern forurenet oxidlag med HF syre fortyndes i vand (10: 1, 3-4 min, ætsehastighed ≈ 40 nm / min ved 30 ° C), skylles i deioniseret vand (10 min).

- Oxidere som i 1.1.2.

- Udføre fotolitografi og etch oxid.

- Gate Oxide

- Gentag trin 1.2.1 og 1.2.2.

- Placer wafer i dedikeret ovn ved 800 ° C og oxidere i trin som følger: tør O 2 (10 min), dichloroethylene + O 2 (20 min), tør O 2 (10-30 min afhængig af den ønskede oxid tykkelse), N2 (15 min).

- Ohmske kontakter Metallisering

- Gentag trin 1.2.1.

- Placer wafer i elektron-beam fordamperen. Fordampe 100 nm af aluminium på 0,2-0,5 nm / sek og 5 x 10 -6 Torr.

- Soak skiven i N-methyl-2-pyrrolidon (NMP) på varmeplade ved 80 ° C i 1 time for at løfte metallet. Bruge ultrasonisk omrøring hvis nødvendigt. Skyl i IPA i 2 min. Blow tørt med N2.

- Annealer ved dannelse gas ved 400 ° C i mindst 15 min.

2. nanofabrikation

- Wafer Dicing

- Spin nogen modstå på wafer at fungere som beskyttende belægning (type af polymer og spinning parametre er irrelevant i denne fase).

- Bruge diamant spids dicer at skære skiven i individuelle chips af ~ 10 x 2 mm2.

- Rengøring

- Blød i NMP i 1 time på varmeplade ved 80 ° C, derefter skylles i IPA i 2 min. Blow tørt med N2.

- Udfør O 2 plasma etch i 5 min (indfaldende effekt = 50 W; reflekteret effekt <1 W).

- Spin ren med acetone og IPA (7500 rpm, 30 sek)

- Justeringsmærkerne mønster

- Spin polymethylmethacrylat (PMMA 950k) A4 modstå (5,000-7,500 rpm, 30 sek afhængigt af den ønskede tykkelse). Typisk arbejdsdag tykkelse ≈ 150-200 nm. Bage resisten på en varmeplade ved 180 ° C i 90 sek.

- Udfør e-beam litografi. Brug følgende skrive betingelser: beam energi = 30 keV, strålestrømmen ≈ 30 Pa, dosis område ≈ 500-650 pC / cm2 afhængig markører størrelse og modstå tykkelse.

- Udvikle resisten i en opløsning af methylisobutylketon og IPA (1: 3) til 40-60 sek, derefter skylles i IPA i 20 sekunder. Blow tørt med N2 pistol.

- Stedchippen i elektron-beam fordamperen. Fordampe 15 nm af Ti og 65 nm af Pt på 0,2-0,4 nm / sek og 5 x 10 -6 Torr.

- Løft metal som i trin 1.4.3.

- Ren chip som i trin 2.2.2-2.2.3.

- Gate mønster

- Spin modstå som i 2.3.1.

- Udfør e-beam litografi. Brug følgende skrive betingelserne for høj opløsning funktioner: beam energi = 30 keV, strålestrømmen ≈ 30 Pa, dosis område ≈ 500-700 pC / cm2. Skriv betingelser for lav opløsning funktioner: stråleenergi = 15 keV, strålestrømmen ≈ 10 nA, dosis område ≈ 400-600 pC / cm2.

- Udvikle modstå som i 2.3.3.

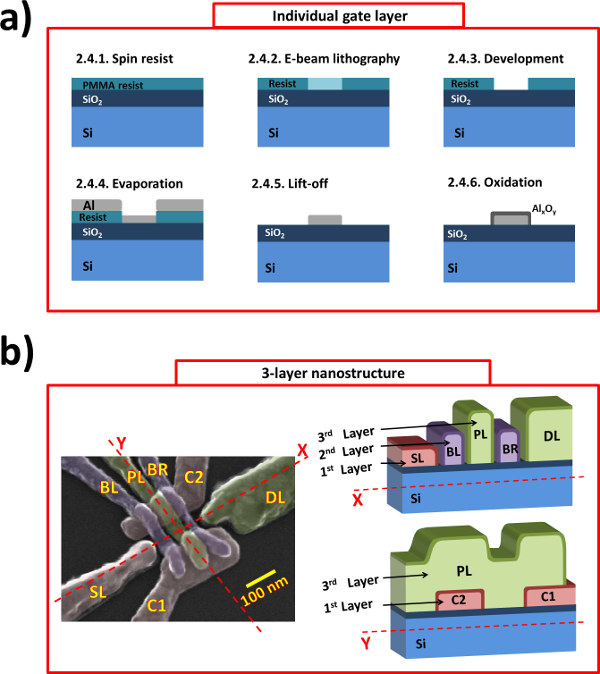

- Placer chippen i termisk fordamper. Fordampe Al på 0,1-0,4 nm / sek og 1-9 x 10 -6 mbar. Mål tykkelse varierer efter lag nummer, som vist i figur 2B (25-35 nm for Lag 1, 45-65 nm for Layer 2, 75-90 nm for Layer 3).

- Løft metal som i trin 1.4.3.

- Udfør Al oxidation på en varmeplade ved 150 ° C i 5-10 min.

- Ren chip som i trin 2.2.3.

- Gentag trin 2.4.1-2.4.7 to gange for at realisere 3-lags gate stakken.

3. Enhed Emballage

- Terninger chip som i trin 2.1

- Skyl de deraf mindre chips i acetone og IPA i 2 min.

- Lim en individuel brik til et trykt kredsløbskort (PCB) med PMMA A5. Vente 2 min for det tørre. Alternativt, for at øge thermalization bruge sølv epoxy.

- Indlæse PCB på en kile Bonder og fortsætte med ledninger.

4. Enhedens Integrity Tests

- Monter PCB indeholder det kablede enhed på en dukkert sonde.

- Wire elektriske linjer af PCB til de af dip sonden.

- Indsætte sonden i en beholder indeholdende flydende helium. Gå langsomt for at undgå overdreven helium Bolie-off.

- For hver enhed gate, tilslut den tilsvarende stuetemperatur elektrode af sonden til en kilde mål enhed, samtidig med at de andre porte jordet. Indstil overholdelse strøm til nogle nA. Fej spændingen fra nul til 1.5V i trin på 0,1 V, måle og registrere den aktuelle.

- Forbinde hver gate linje til en batteridrevet variabel DC spændingskilde, kilden linje til den indbyggede AC spænding kilde af en lock-in forstærker, og afløbsrør til indgangsporten af lock-in forstærker.

- Mål kilde til at dræne konduktans for forskellige gate spænding konfigurationer (se figur 4).

- Globalt rampe op spændingerne anvendes på porte BL, BR, PL, SL og DL, ved at holde C1 og C2 porte jordet. Optage de "turn-på 'Enhed karakteristika.

- Individuelt rampe ned hver gate spænding og registrere portene 'pinch-off' karakteristika.

- Justere gate spændinger på elektrostatisk definere en quantum prik ved at sætte de spændinger på BL og BR (PL, SL og DL) mindre (større) end turn-on spændinger. Optage Coulomb blokade egenskaber.

Representative Results

Enhed Fabrication

Den indledende mikrofabrikation proces (underafsnit 1 i protokollen) udføres på et kommercielt 4-inch høj renhed silicium wafer (n-type doping koncentration ≈ 10 12 cm -3, resistivitet> 10 kΩcm; tykkelse = 310-340 um ). Målet er at realisere substrat, hvorpå gateelektroderne vil blive deponeret. Dette substrat er fremstillet af en indre region udjævnet med felt oxid (trin 1.1), en n + region udjævnet med felt oxid (trin 1.2), en indre region capped med høj kvalitet gate-oxid (trin 1.3), og et metalliseret n + region for ohmske kontakter (trin 1.4). Figur 1A-D viser de vigtigste trin i processen mikrofabrikation. Figur 1E viser en mikroskopisk billede af et substrat marken efter mikrofabrikation. Den mindste funktion størrelse for litografi på dette trin er ca. 4 um.

SiO2 oxidlag dyrkes i trin 1.1 har en nominel tykkelse på 100 nm og anvendes som et passiveringslag. De n-type-områderne, der virker som ohmske ledere opnås via phosphor diffusion. Målet doping massefylde er ca 19 OKTOBER - 20 OKTOBER cm -3. Den høje kvalitet SiO2, som er selektivt dyrket til anvendelse som gate dielektrikum har en nominel tykkelse på 5 nm. Målet grænseflade defekt massefylde er <10 10 eV -1 cm -2 medio hul. En dedikeret og med vilje bygget tredobbelt væg ovn bruges til denne proces. Dette system er designet til at minimere forurening fra tunge metalioner og mobile alkaliioner, samt forhindre fugt i at diffundere ind i oxidation kammeret. For at danne de elektriske kontakter, er aluminium pads aflejret via elektronstråle fordampning på en del af de n-type-områderne.

Den nanofabrikation (se underafsnit 2) udføres på chip substrates opnået ved terninger skiven behandles i trin 1. Formålet er at realisere nanoskala gateelektroder bruges til elektrostatisk definere MOS QDs. Hver nanofabrikation køre typisk producerer 10-15 komplette enhed prøver. Scanningselektronmikrografi (SEM) billeddannelse af 1-2 enheder pr batch udføres sædvanligvis at bekræfte, at EBL litografi faser har været vellykkede. Da SEM billeddannelse kan injicere afgifter i substratet eller i de metalliske porte og forårsage lækager, er kun et lille antal enheder kontrolleres på denne måde, mens resten er elektrisk testes. Mindste funktion størrelse for litografi på dette trin er ca. 35 nm. At opnå en god ensartethed af de deponerede Al film bliver metallet fordampes ved priser så langsom så få Ångstrøm / sekund, mens substratet er monteret på en roterende scene. Dette holdes ved stuetemperatur, og Al kornstørrelse skønnes at være på ca. 20 nm. Figur 2A viser de vigtigste trin i nanofabrication proces. Figur 2B viser et SEM-billede, med hvilken den korrekt definition af gateelektroderne verificeres. Generelt ét formål at realisere de porte, der direkte definerer QD (BL, BR og PL) med den mindst mulige funktion størrelse. Derimod kan disse porte anvendes til at definere de elektron reservoirer (DL og SL) har større dimensioner for at undgå utilsigtet diskretisering af energiniveauer i ledningerne. Nanoskala Ti / Pt markører realiseret i trin 2.3 anvendes som reference for konsekvent tilpasning af de tre lag af porte. Platin er valgt for sin fremragende kontrast i forhold til SiO2 overflade i e-beam. Titanium bruges til at forbedre vedhæftning.

I alle faser af produktionsprocessen, er carbon-fiber-tip pincet bruges til at håndtere de chips, med henblik på at reducere sandsynligheden for destruktive elektrostatisk afladning (ESD).

Endelig, for at udføre elektriske målinger på enkelte kdobbelte enheder, skal spaltes i mindre stykker på ca. 2 x 2 mm 2 (underafsnit 3) hver chip. Hvert stykke bliver så limet til en skræddersyet PCB (Rogers R03010 lavt tab dielektriske), hvis ben er forbundet til enheden elektroder gennem Al ledninger. Wire bonding udføres med en kile Bonder maskine uden opvarmning af chips. Valget af de relevante limning parametre er baseret på to betragtninger. På den ene side, wiren binding nødt til at perforere den termiske Al y O x lag og gøre god metal-til-metal kontakt med porten pad. På den anden side kan en overdreven mekanisk belastning medføre en punch-trough begivenhed, som skader feltet oxid under porten og forårsage substrat lækager. Under forbindelsesprocessen, er tilrådeligt at forhindre ESD anvendelsen af et antistatisk armbånd. I figur 3 er en chip med 6 individuelle enheder limet på printkortet.

Device integritet tests

Before indlæsning af en enhed til en mK temperaturmåling platform såsom en fortynding køleskab, er foreløbige elektriske tests udført ved 4,2 K for at kontrollere integriteten af prøven (se underafsnit 4 i protokollen). Til dette formål er printet indsat i et oxygenfrit kobber kabinet og er monteret på et dip probe, som vinder nedsænket i flydende He.

Den første prøvning er typisk en lækagetest, der udføres sekventielt på hver port. En kilde-mål er tilsluttet til en individuel gate-elektrode, medens de andre er jordet. Spændingen bliver hævet til 1,5 V og strømmen måles ved kilden. Inden for dette spændingsområde er et velfungerende port ikke meningen at gennemføre, fordi SiO2 lag isolerer metal fra silicium substrat og Al y O x isolerer overlappende porte. Typisk oxid opdeling vides at forekomme for spændinger større end ~ 4 V, afhængigt af enhedens geometri og oxid thickness. Derfor, hvis der registreres strøm under testen, er det sandsynligt, at i det mindste en af oxidlag er beskadiget, og anordningen skal kasseres. Sædvanligvis mindre end 10% af portene viser lækager. Udbyttet er kendt for at blive påvirket af den plane forlængelse af gateelektroderne. Især den større overlapning af portene med gateoxiden region jo mere sandsynligt vil være at have gate-til-substrat utætheder. Tilsvarende vil større overlapning mellem portene fra forskellige lag jo mere sandsynligt at forekomsten af gate-til-gate lækager være. Den citerede udbytte er relevant for porte, der optager et areal på omkring 50 um 2 på den tynde oxid og med mellemlag overlapninger på ca. 0,5 um 2.

Når enheden har passeret den første tæthedsprøvning, er kilden og drain kontakter forbundet til en lock-in forstærker og portene til en modulær kontrollerbar spænding batteri rack. I denne konfiguration er enheden drejes on ved globalt rampe op alle gate spændinger samtidigt. Dernæst bliver hver gate spænding separat ramped ned samtidig holde de andre på høje spændinger for at verificere evnen af individuelle porte for at afklemme den nuværende. Figur 4A viser repræsentative spor af disse målinger. Fraværet af enten en source-drain overledning pathway eller individuel gate pinch-off er ofte en indikation af nogle type gate skader såsom gate eksplosion eller metal diskontinuitet.

Endelig er det source-drain strøm målt som en funktion af source-drain bias og stemplet gate spænding for at observere undertegnelsen af Coulomb blokade 16 (se figur 4B).

Målinger

Når en egnet anordning er fundet, fjernes fra væsken Han fartøj, og tørret med en varmepistol for at undgå dannelse af fugt, som kan forårsage ESD. Endelig overføres det til en fortynding køleskab.

<p class = "jove_content"> Forsøgene udføres i en self-made plastik fortynding køleskab med en base temperatur på ca. 100 mK. Kryostaten er i et vakuumkammer nedsænket i en 4,2 K helium bad. De elektriske linjer thermalized på 1 K potten som også anvendes til at kondensere den indkommende 3He damp. I blandekammeret, den endoterme overførsel af 3He atomer fra 3He-rige fase i 3He-fortyndet fase giver systemet mulighed for at nå en base temperatur på ca. 100 mK.Som vist i figur 5, er køleskabet udstyret med 20 dc linjer og 3 rf linjer bruges til at forbinde stuetemperatur elektronik til enheden ved lav temperatur. Fem af dc linjer er Thermocoax kabler og 15 parsnoet væven ledninger. Disse linjer forbinder gate elektroder af prøven til batteridrevne dc spænding kilder. Spændingsdelere ved stuetemperatur anvendes til at reducere elektrisk støj på individuelle porte. RF linjer er halvstive koaksialkabler, der er dæmpet med 10 dB ved 4 K for at reducere termiske støj og blokeret ved RT dc. Disse linjer er forbundet til de koplanare bølgeledere af bias tees på printet.

En lav-støj transimpedance forstærker og et digitalt multimeter anvendes til at måle den strøm, der genereres af pumpen. Elektronikindustrien er forbundet til enheden via batteridrevne optoisolators at forhindre dannelsen af jordsløjfer. Signalerne RF drev er fremstillet efter en vilkårlig bølgeform generator hvis jordforbindelse er isoleret fra en af kryostaten via en DC blok komponent (se figur 5).

Den PCB indeholder 16 rene dc linjer og 4 skævhed tee linjer anvendt til at kombinere DC og AC spænding ved lav temperatur. Som vist i figur 3B, er RC diskrete komponenter benyttes til at udnytte tee-forbindelse (R = 100 kohm, C = 10 nF), og 50 Ω-matchede integrerede koplanare bølgeledere anvendes til formering af højfrekvente signaler.

e_content "> Når enheden er i mK temperatur, er porten spændinger justeres, således at en enkelt elektron belægning i QD er nået. Især er barrierer tunnel dannes under porte BL og BR, og en elektron ophobning lag induceres under porte PL, SL og DL. Til dette formål de barriere gate spændinger er sat under deres turn-på værdier, mens ophobning porte er polariseret i en større-end-turn-on spænding. På denne måde en QD dannes under porten PL og dets plane forlængelse styres via gates C1 og C2, hvis spændinger holdes under deres tur-på værdier til at inducere elektrostatiske indeslutning. Dernæst RF signaler tændt til periodisk modulere gennemsigtighed af tunnelen barriere (r), og den elektrokemiske potentiale prik. Single-elektron pumpning opnås med enten en eller to sinusformede drivende spændinger. I tilfælde af en-signal drev, er den drivende påtrykkes gate BL at modulere potentialet af tunnelen dæmningen ved den venstre -SIDE afQD. I tilfælde af to-signal drev, er ac excitationer anvendes på porte BL og PL at modulere potentialerne i både venstre barrieren og QD på samme frekvens men med forskellige faser og amplituder. Disse yderligere frihedsgrader tillader en at styre retningen af elektronoverførsel 13. En iterativ proces er typisk nødvendig for at tune de vigtigste eksperimentelle parametre (dvs. rf drev signalamplituder / faser og dc gate spændinger) og opnå en optimal strøm kvantisering. Bemærk, at ingen af de to pumpestationer protokoller brug for en drain-source forspænding til at udføre charge overførsler. Derfor er kilde- og drænelektroderne jordet under pumpens drift. Figur 6 viser den karakteristiske aktuelle plateauer ved hele multipla af ef opnået ved at anvende en to-signal sinusformet drev til indgangen barriere (BL) og stemplet (PL) gate. Disse data er taget ved en relativt lav drivende frekvens (10 MHz), hvor t indstillingsmenu af parametrene kan udføres hurtigt. I praksis er det ønskeligt at drive pumpen ved flere hundrede MHz, typisk kræver en meget finere parameter optimering 13.

Figur 1. mikrofabrikation. (A) Skematisk illustration af de vigtigste skridt i mikrofabrikation. Tegnefilm er ikke tegnet i skala. (B) Realisering af en doteret region for ohmske kontakter. (C) Realisering af gate-oxid. (D) Metallisering af ohmske kontakter. (E) Mikroskopisk billede af et enkelt felt på en chip efter mikrofabrikation er afsluttet. Felt størrelse er 1,2 x 1,2 mm 2. Klik her for at se en større version af dette tal.

Figur 2. nanofabrikation. (A) produktionsprocessen for individuelle gate lag. Tegnefilm er ikke tegnet i skala. (B) Det 3-lags gate nanostruktur bruges til opladning pumpe eksperimenter. Venstre: SEM billede af en anordning i lighed med den, der anvendes til målingerne. Til højre:. Skematisk tværsnit af indretningen på tværs X-cut og Y-cut Klik her for at se en større version af dette tal.

Figur 3. Elektriske forbindelser til prøven. (A) Opstilling af printkortet. (B) forstørrelse af et område af PCB med en bias-tee (venstre) end tilsvarende kredsløb (højre). (C) En chip med 6 individuelle felter limet på chippen holder og bond ledninger til elektrisk forbindelse med printpladen. (D) Mikroskopisk billede af en individuel felt efter nanofabrikation. (E) SEM billede af porten layout i midten af porten oxid-regionen. Klik her for at se en større version af dette tal.

Figur 4. Foreløbige tests. (A) Kilde-drain vekselstrøm (root mean square) som en funktion af forskellige gate spændinger. Spor måles med en lock-in forstærker med 50 μV RMS excitation ved 113,17 Hz. Til individuel gate spænding spor de resterende gate spændinger fastsat til 2,0 V, med undtagelse af V C1 = <em> V C2 = 0,0 V. (B) Farve kort over source-drain strøm som en funktion af stempel gate spænding og source-drain forspænding. V SL = 1,5 V, V DL = 1,15 V, V BL = 0,78 V, V BR = 0,85 V, V C1 = V C2 = 0,0 V. Klik her for at se en større version af dette tal.

Figur 5. Skematisk af målingen set-up. Tyve dc linjer (grøn) og tre koaksiale rf linjer (sort) forbinder RT elektronik til PCB. Afløbet for pumpen (lilla) er forbundet med en overføringsimpedansforstærker og en digital multimeter via en optoisolator, mens kilden kontakt (rød) er jordet. Separate jordforbindelser (indicated med forskellige symboler) anvendes til elektronisk instrumentering og kryostaten elektriske ledninger. Klik her for at se en større version af dette tal.

Figur 6. Aktuel kvantisering. Pumped strøm som funktion af V PL for to-signal sinusformet drev ved f = 10 MHz anvendes på porte BL og PL. Faseforskel = 49 grader, V RF PL = V RF BL = 0,31 V pp. Den ideelle placering af pumpe plateauer ved heltal multipla af ef vises som røde vandrette linjer. Klik her for at se en større version af dette tal.

Discussion

Protokollen rapporteret i dette papir beskriver teknikker til at fremstille silicium MOS QDs, samt de eksperimentelle procedurer til at teste deres funktionelle integritet og drive dem som enkelt-elektron pumper. Bemærkelsesværdigt, ved at skræddersy porten design, den samme fremstillingsproces kan anvendes til at fremstille apparater, for quantum bit udlæsning og kontrol 17 samt ladningspumpeorganerne 12,13. Vi bemærker, at mange af de procesparametre citeret i denne artikel kan variere afhængigt af fabrikation værktøjer (kalibrering, mærke eller model), samt af typen af silicium substrat (tykkelse og baggrund doping tæthed). Mængder såsom dosis litografi eksponering eller udviklingstid, ætsning eller oxidering varighed, skal omhyggeligt kalibreret og testet for at sikre en pålidelig udbytte. Desuden er det afgørende at undgå krydskontaminering som følge af brugen af de samme fabrikation værktøjer til forskellige processer. Til dette formål et antal crtiske trin udføres med udstyr udelukkende til silicium forarbejdning, såsom metal fordampere, ilt ovne og HF bade.

Mere generelt er silicium trække en stigende interesse som det foretrukne materiale til at realisere charge pumper 18-20. Dette skyldes til dels den attraktive perspektiv implementere en ny kvante-baserede elektrisk strøm standard ved hjælp af en industri-kompatibel silicium proces. Dette vil have gavn af veletablerede og pålidelige integration teknikker til skalerbarhed, parallelisering og kørsel overhead. Vigtigere er det, en fuld supplerende MOS (CMOS) teknologi, fri for traditionel metal som porten materiale, har vist stærkt reducerede afgift udsving baggrund i single-elektron enheder 21. Sådanne udsving kan være skadelige i at opnå metrologiske nøjagtigheder.

Protokollen diskuteret her er begrænset til realiseringen af MOS nano-enheder med metal porte. Derfor, for at achieve fuld industriel kompatibilitet og reducere charge udsving, ville det være nødvendigt at modificere gate aflejringsteknikker og bruger højt doteret polykrystallinsk silicium som porten materiale.

Afslutningsvis har MOS QD pumperne diskuteret her for nylig kombineret det teknologisk fordel af silicium med meget gode resultater i form af præcise nuværende generation 13. Dette skyldes den høje fleksibilitet af design og fabrikation proces, som tillader en at stable flere gate lag fører til en kompakt og alsidigt system. Det resulterende fine justerbarhed af den elektrostatiske indespærring af dot sammen med potentiale til at reducere baggrund charge udsving sætter scenen for at overvinde de vigtigste udfordringer observeret i andre halvleder pumper 22,23.

Disclosures

Forfatterne har ikke noget at afsløre.

Acknowledgments

Vi takker KY Tan, P. See og GC Tettamanzi for nyttige diskussioner. Vi anerkender økonomisk støtte fra forskningsrådet australske (Grant No. DP120104710), Finlands Akademi (Grant No. 251.748, 135.794, 272.806) og støtte fra Australian National Fabrication faciliteten for enhedens opspind. AR anerkender økonomisk støtte fra University of New South Wales Early Career Forsker Grant ordningen. Tilvejebringelse af faciliteter og teknisk support ved Aalto University på Micronova nanofabrikation Centre er også anerkendt.

Materials

| Name | Company | Catalog Number | Comments |

| Silicon wafers | TOPSIL | 4 inch | |

| Electron-beam lithography machine | Raith gmbh | Raith 150two | |

| E-beam resist | MicroChem gmbh | PMMA | |

| Photoresist | MicroChem gmbh | nLOF2020 | |

| Mask aligner | Quintel | Q6000 | |

| Photoresist developer | MicroChem gmbh | AZ826MIF |

References

- Sze, S. M. Physics of Semiconductor Devices. , Wiley. Interscience, NY. 505-566 (1969).

- Moore, G. E. Cramming More Components onto Integrated Circuits. Electronics. 38, 114-117 (1965).

- Voisin, B., et al. Few-Electron Edge-State Quantum Dots in a Silicon Nanowire Field-Effect Transistor. Nano Lett. 14 (4), 2094-2098 (2014).

- Asenov, A., Brown, A. R., Davies, J. H., Savas, K., Slavcheva, G. Simulation of Instrinsic Parameter Fluctuations in Decananometer and Nanometer-Scale MOSFETs. IEEE Trans Electron Devices. 50 (9), 1837-1852 (2003).

- Zwanenburg, F. A., et al. Silicon Quantum Electronics. Rev. Mod. Phys. 85 (3), 961-1019 (2013).

- Ladd, T. D., et al. Quantum computers. Nature. 464 (7285), 45-53 (2010).

- Piquemal, F. Genevès, G. for a direct realization of the quantum metrological triangle. Metrologia. 37 (3), 207-211 (2000).

- Angus, S. J., Ferguson, A. J., Dzurak, A. S., Clark, R. G. Gate-Defined Quantum Dots in Intrinsic Silicon. Nano Lett. 7 (7), 2051-2055 (2007).

- Gonzalez-Zalba, M. F., Heiss, D., Podd, G., Ferguson, A. J. Tunable aluminium-gated single electron transistor on a doped silicon-on-insulator etched nanowire. Appl. Phys. Lett. 101 (10), 103504-103501 (2014).

- Lim, W. H., et al. Observation of the single-electron regime in a highly tunable silicon quantum dot. Appl. Phys. Lett. 95 (24), 242102-242103 (2009).

- Yang, C. H., et al. Spin-valley lifetimes in silicon quantum dots with tunable valley splitting. Nat. Commun. 4 (2069), (2013).

- Chan, K. W., et al. Single-electron shuttle based on a silicon quantum dot. Appl. Phys. Lett. 98 (21), 212103-212101 (2011).

- Rossi, A., et al. An accurate single-electron pump based on a highly tunable silicon quantum dot. Nano Lett. 14 (6), 3405-3411 (2014).

- Pekola, J. P., et al. Single-electron current sources: Toward a refined definition of the ampere. Rev. Mod. Phys. 85 (4), 1421-1472 (2013).

- Giblin, S. P., et al. Towards a quantum representation of the ampere using single electron pumps. Nat. Commun. 3, 930 (2012).

- Kouwenhoven, L. P., Austing, D. G., Tarucha, S. Few-electron quantum dots. Rep. Prog. Phys. 64 (6), 701-736 (2001).

- Veldhorst, M., et al. An addressable quantum dot qubit with fault-tolerant control fidelity. Nat. Nanotech. 9 (12), 981-985 (2014).

- Fujiwara, A., Nishiguchi, K., Ono, Y. Nanoampere charge pump by single-electron ratchet using silicon nanowire metal-oxide-semiconductor field-effect transistor. Appl. Phys. Lett. 92 (4), 042102-1-042102-3 (2008).

- Jehl, X., et al. Hybrid Metal-Semiconductor Electron Pump for Quantum Metrology. Phys. Rev. X. 3 (2), 021012-1-021012-7 (2013).

- Tettamanzi, G. C., Wacquez, R., Rogge, S. Charge pumping through a single donor atom. New J. Phys. 16 (6), 063036-1-063036-17 (2014).

- Koppinen, P. J., Stewart, M. D., Zimmerman, N. M. Fabrication and Electrical Characterization of Fully CMOS-Compatible Si Single-Electron Devices. IEEE Trans Electron Devices. 60 (1), 78-83 (2013).

- Fletcher, J. D., et al. Stabilization of single-electron pumps by high magnetic fields. Phys. Rev. B. 86 (15), 155311-1-155311-6 (2012).

- Kataoka, M., et al. Tunable Nonadiabatic Excitation in a Single-Electron Quantum Dot. Phys. Rev. Lett. 106 (12), 126801-1-126801-4 (2011).