Protocol

Opmerking: Dit protocol beschrijft de procedures voor het vervaardigen, verpakken en testen van één elektron pomp op basis van silicium MOS QD techniek. De stappen besproken in de paragrafen 1 en 2 zijn opgenomen in een ISO5 cleanroom uitgevoerd, terwijl die van deel 3 worden uitgevoerd in ISO6 laboratoria. Omgevingscondities worden voortdurend gecontroleerd. Nominale waarden voor de temperatuur en luchtvochtigheid zijn ingesteld op 20 ± 1 ° C en 55% ± 5%, respectievelijk.

1. Microfabricage

- Field Oxide

- Reinig de wafer door onderdompeling in het volgende: piranha ets (10 min), gedeïoniseerd (DI) water (10 min), RCA-2-oplossing (175 ml gedeïoniseerd water, 30 ml HCl, H 2 O 2 30 ml bij 100 ° C gedurende 10 min), gedeïoniseerd water (5 min), waterstoffluoride (HF) zuur verdund in water 10: 1 (10 sec), DI water (10 min). Gebruik beschermende kleding bij het werken met HF (dwz veiligheidsbril, PVC schort, en PVC handschoenen). Ga in de aangegeven volgorde.

- Plaats de waferoxidatie oven bij 900 ° C en oxideren stapsgewijs als volgt: droog O 2 (10 min), nat O 2 (40 min), droog O 2 (10 min), 2 N (15 min).

- Ohmse contacten

- Voeren fotolithografie en etsen oxide.

- Borg enkele-nm dikke laag hechtprimer hexamethyldisilazaan (HMDS) op het wafeloppervlak als volgt: pre-bakken op een verwarmingsplaat bij 110 ° C gedurende 1 min, pour ~ 50 ml HMDS in een glazen beker, het bekerglas en de wafel in de vacuümkamer, evacueren en wacht 2 min.

- Spin 2-4 urn dikke laag van fotolak zowel achter en voorzijden van de wafel (3000-5000 rpm, 25-40 sec afhankelijk van de gewenste dikte).

- Blootstellen aan ultraviolet licht in mask aligner (10 mW / cm2 gedurende 4-10 seconden afhankelijk van de dikte weerstaan). Post-bakken op een verwarmingsplaat bij 110 ° C gedurende 1 min.

- Ontwikkelen voor 1-2 minuten, dan afspoelen in gedeïoniseerd water. Voer O 2 plasma etsen gedurende 20 min (druk = 340 mTorr; incident vermogen = 50 W; gereflecteerde vermogen <1 W).

- Etch oxyde in een gebufferde HF-oplossing (15: 1, 4-5 min, etssnelheid ≈ 20 nm / min bij 30 ° C). Spoelen met gedemineraliseerd water (5 min). Blaas droog met N2.

- Verwijder fotoresist door onderdompeling in aceton. Spoel in isopropanol (IPA), daarna föhnen met N2.

- Plaats wafer in oven bij 1000 ° C met fosforbron (N2-stroom gedurende 30-45 minuten afhankelijk van de gewenste dichtheid doping).

- Verontreinigde oxidelaag met HF zuur verdund in water (10: 1, 3-4 min, etssnelheid ≈ 40 nm / min bij 30 ° C), spoelen met gedeïoniseerd water (10 min).

- Oxideren zoals in 1.1.2.

- Voeren fotolithografie en etsen oxide.

- Gate Oxide

- Herhaal stap 1.2.1 en 1.2.2.

- Plaats wafer in speciale oven bij 800 ° C en oxideren stapsgewijs als volgt: droog O 2 (10 min), dichloroethylene + O 2 (20 min), droog O 2 (10-30 min afhankelijk van de gewenste dikte oxide), N 2 (15 min).

- Ohmse contacten Metalliseren

- Herhaal stap 1.2.1.

- Plaats de wafer in electron-beam verdamper. Damp 100 nm aluminium op 0.2-0.5 nm / sec en 5 x 10 -6 Torr.

- Week de wafer in N-methyl-2-pyrrolidon (NMP) op verwarmingsplaat bij 80 ° C gedurende 1 uur te heffen van het metaal. Ultrasone agitatie indien nodig. Spoel in IPA gedurende 2 min. Blaas droog met N2.

- Ontlaten bij het vormen van gas bij 400 ° C gedurende ten minste 15 min.

2. Nanofabrication

- Wafer Dicing

- Draai elk resist op de wafer om als beschermende coating (type polymeer en spinparameters irrelevant op dit moment).

- Gebruik diamond tip snijmachine aan de wafer in individuele chips van ~ 10 x 2 mm 2 te snijden.

- Schoonmaak

- Weken in NMP gedurende 1 uur op verwarmingsplaat bij 80 ° C en spoel in IPA gedurende 2 min. Blaas droog met N2.

- Voer O 2 plasma etsen gedurende 5 min (incident vermogen = 50 W; gereflecteerde vermogen <1 W).

- Spin schoon met aceton en IPA (7.500 rpm, 30 sec)

- Alignment markers patroonvorming

- Spin polymethyl methacrylaat (PMMA 950K) A4 weerstaan (5,000-7,500 rpm, 30 seconden afhankelijk van de gewenste dikte). Typische dikte werkende ≈ 150-200 nm. Bak de resist op een verwarmingsplaat bij 180 ° C gedurende 90 sec.

- Het uitvoeren van e-beam lithografie. Gebruik de volgende write voorwaarden: stralingsenergie = 30 keV, straalstroom ≈ 30 pA, dosis gebied ≈ 500-650 uC / cm2, afhankelijk van de grootte markers en weerstaan dikte.

- Ontwikkelen van de resist in een oplossing van methyl isobutyl keton en IPA (1: 3) gedurende 40-60 sec, spoel in IPA gedurende 20 sec. Blaas droog met N 2 pistool.

- Plaatsde chip in electron-beam verdamper. Damp 15 nm van Ti en 65 nm van Pt op 0,2-0,4 nm / sec en 5 x 10 -6 Torr.

- Til de metalen zoals in stap 1.4.3.

- Clean chip als in de stappen 2.2.2-2.2.3.

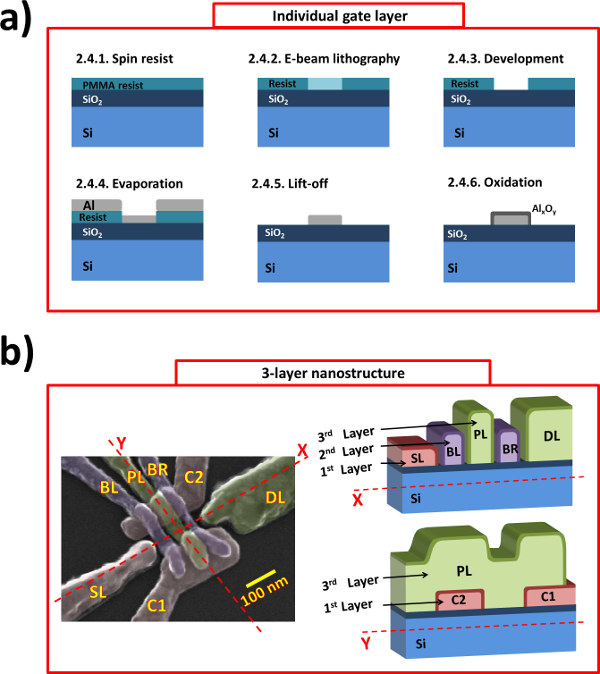

- Gate patroonvorming

- Spin verzetten zoals in 2.3.1.

- Het uitvoeren van e-beam lithografie. Gebruik de volgende write voorwaarden voor hoge resolutie features: stralingsenergie = 30 keV, straalstroom ≈ 30 pA, gebied dosis ≈ 500-700 uC / cm2. Schrijf voorwaarden voor lage resolutie features: stralingsenergie = 15 keV, straalstroom ≈ 10 nA, gebied dosis ≈ 400-600 uC / cm2.

- Ontwikkel de weerstaan als in 2.3.3.

- Plaats de chip thermische verdamper. Verdampen Al bij 0,1-0,4 nm / sec en 1-9 x 10 -6 mbar. Doeldikte varieert laagaantal, zoals getoond in Figuur 2B (25-35 nm voor Layer 1, 45-65 nm voor Layer 2, 75-90 nm voor Layer 3).

- Til de metalen zoals in stap 1.4.3.

- Al voeren oxydatie op een verwarmingsplaat bij 150 ° C gedurende 5-10 min.

- Clean chip als in stap 2.2.3.

- Herhaal de stappen 2.4.1-2.4.7 twee keer om de 3-layer gate stack te realiseren.

3. Inrichting Packaging

- Dice chip als in stap 2.1

- Spoel de resulterende kleinere chips in aceton en IPA gedurende 2 min.

- Lijm een individueel stuk om een printed circuit board (PCB) met PMMA A5. Wacht 2 min tot het droog is. Als alternatief voor thermalisatie verbeteren, gebruik zilver epoxy.

- Laad de PCB op een wig bonder en ga verder met de bedrading.

4. Device Integrity Tests

- Monteer de PCB-houdende het bedrade apparaat op een dip probe.

- Sluit de elektrische leidingen van de PCB die de dip probe.

- Steek de sonde in een vat met vloeibaar helium. Ga langzaam aan overmatige helium b voorkomenolie-off.

- Voor elk apparaat poort, sluit de bijbehorende kamertemperatuur elektrode van de sonde naar een bron-maatregel unit, terwijl de andere poorten geaard. Stel de naleving stroom naar enkele nA. Veeg de spanning van nul tot 1,5 V in stappen van 0,1 V, meten en registreren van de stroom.

- Sluit elke poort lijn naar een batterij-aangedreven variabele dc spanningsbron, de bron lijn naar de ingebouwde wisselspanning bron van een lock-in versterker en de afvoerleiding naar de ingangspoort van de lock-in versterker.

- Meet de bron tot conductantie uitlekken verschillende gate voltage configuraties (zie figuur 4).

- Wereldwijd opvoeren van de spanningen toegepast op poorten BL, BR, PL, SL en DL, door het houden van C1 en C2 poorten geaard. Noteer de 'turn-on' kenmerken van het apparaat.

- Individueel uitloop elke gate spanning en noteer kenmerken de poorten 'pinch-off'.

- Stel de poort spanningen een Qu elektrostatisch definiërenantum dot door de spanningen op BL en BR (PL, SL en DL) kleiner (groter) dan de turn-on spanning. Noteer de Coulomb blokkade kenmerken.

Representative Results

Device Fabrication

De initiële microfabricage proces (onderdeel 1 van het Protocol) wordt uitgevoerd op een commercieel 4-inch hoge zuiverheidsgraad silicium wafer (n-type dotering ≈ 10 12 cm -3; weerstand> 10 kΩcm; dikte = 310-340 um ). Doel is het substraat waarop de poortelektroden worden aangebracht realiseren. Het substraat bestaat uit een intrinsiek gebied afgedekt met veldoxide (stap 1,1), een n + gebied afgedekt met veldoxide (stap 1,2), een intrinsieke gebied afgedekt met hoogwaardige gate oxide (stap 1.3) en een gemetalliseerd n + regio ohmse contacten (stap 1.4). figuren 1A-D illustreren de belangrijkste stappen van de microfabricage proces. een microscopisch beeld van een substraat veld Figuur 1E toont na microfabrication. De minimale eigenschap afmeting van de lithografie in dit stadium is ongeveer 4 urn.

De SiO2 oxidelaag gegroeid in stap 1.1 een nominale dikte van 100 nm en wordt gebruikt als een passiveringslaag. De n-type gebieden die als ohmse geleiders worden verkregen via fosfor diffusie. Het doel doping dichtheid ongeveer 19 oktober - 20 oktober cm -3. De hoogwaardige SiO 2 die selectief wordt gekweekt voor gebruik als poortdielektrikum een nominale dikte van 5 nm. Het doel-interface defect dichtheid <10 10 eV -1 cm -2 halverwege de kloof. Een toegewijd en doelbewust gebouwd triple muur oven wordt gebruikt voor dit proces. Dit systeem is ontworpen om contaminatie door zware metaalionen en mobiele alkali ionen minimaliseren voorkomen alsmede vocht diffundeert in de oxidatiekamer. Om de elektrische contacten gevormd zijn aluminium pads afgezet via elektronenbundel verdamping op een deel van het n-type gebieden.

De nanofabricage proces (zie paragraaf 2) wordt uitgevoerd op chip substrAtes verkregen door dobbelen het verwerkt in stap 1. Het doel wafer is om de nano-schaal gate elektroden gebruikt om de MOS QDs elektrostatisch definiëren realiseren. Elke nanofabricage run produceert gewoonlijk 10-15 complete inrichting monsters. Aftastelektronmicrofoto (SEM) beeldvorming van 1-2 inrichtingen per batch wordt gewoonlijk uitgevoerd om te bevestigen dat de EBL lithografie fasen geslaagd. Omdat SEM beeldvorming ladingen in het substraat of in de metallische poorten kunnen toedienen en lekkages veroorzaken, wordt slechts een klein aantal inrichtingen op deze manier gecontroleerd, terwijl de rest elektrisch getest. Minimale feature size voor de lithografie in dit stadium is ongeveer 35 nm. Voor een goede uniformiteit van de afgezette films Al bereiken, wordt het metaal verdampt met een snelheid zo langzaam weinig angstrom / seconde, terwijl het substraat op een roterende podium is geplaatst. Dit wordt bewaard bij kamertemperatuur, en de Al korrelgrootte wordt geschat ongeveer 20 nm te zijn. Figuur 2A illustreert de belangrijkste stappen van de nanofabrication proces. Figuur 2B toont een SEM opname waarmee de correcte definitie van de poortelektroden wordt gecontroleerd. In het algemeen één gericht op het realiseren van die poorten die direct de QD define (BL, BR en PL) met de kleinst mogelijke feature size. Daarentegen kunnen deze poorten gebruikt om het elektron reservoirs (DL en SL) definiëren grotere afmetingen een onbedoeld discretisatie van energieniveaus in de leidingen te vermijden. De nano-schaal Ti / Pt markers gerealiseerd in stap 2.3 worden gebruikt als referentie voor een consistente uitlijning van de drie lagen van de poorten. Platina wordt gekozen voor zijn goede contrast ten opzichte van het SiO 2 oppervlak in de elektronenbundel. Titanium wordt gebruikt om de hechting te verbeteren.

In alle fasen van het fabricageproces, worden carbon-fiber-tip pincet gebruikt voor de hantering van de chips, ten einde de kans op destructieve elektrostatische ontlading (ESD) verminderen.

Tenslotte, om elektrische metingen ind verrichtendual inrichtingen, elke chip te worden gesplitst in kleinere stukken van ongeveer 2 x 2 mm 2 (paragraaf 3). Elk stuk wordt dan gelijmd op een op maat gemaakte PCB (Rogers R03010 low-loss diëlektrische) waarvan de pennen zijn verbonden met de inrichtingselektroden via Al draden. Wire bonding wordt uitgevoerd met een wig bonder machine uitgevoerd zonder verwarming van de chips. De keuze van de geschikte hechting parameters berust op twee overwegingen. Aan de ene kant, de draadband moet de thermische Al yo x-laag perforeert maken goede metaal-op-metaalcontact met de poort pad. Anderzijds kan een overmatige mechanische belasting tot een punch-trog gebeurtenis die schade toebrengt aan het veldoxide onder het hek en veroorzaken substraat lekkages. Tijdens het bedradingsproces, het gebruik van een antistatische armband is raadzaam om ESD te voorkomen. In figuur 3 wordt een chip met 6 afzonderlijke apparaten gelijmd op de printplaat.

Integriteit apparaat testen

Before laden van een apparaat in een mK temperatuurmeting platform zoals een verdunning koelkast, zijn voorlopige elektrische testen uitgevoerd op 4,2 K om de integriteit van het monster (zie paragraaf 4 van het Protocol) te controleren. Hiertoe wordt de printplaat in een zuurstofvrije koper behuizing geplaatst en wordt op een dip probe, die uiteindelijk wordt ondergedompeld in vloeibare hij gemonteerd.

De eerste test is typisch een lektest die wordt uitgevoerd achtereenvolgens op elke poort. Een source-meeteenheid is aan een afzonderlijke poortelektrode terwijl de anderen geaard. De spanning wordt opgevoerd tot 1,5 V en de stroom wordt gemeten aan de bron. Binnen dit spanningsbereik, is een goed werkende poort niet verondersteld uit te voeren, omdat de SiO 2 laag isoleert het metaal van het silicium substraat en Al y O x isoleert overlappende poorten. Typisch wordt uitgesplitst oxide bekend voorkomt voor spanningen groter dan 4 ~ V, afhankelijk van de geometrie inrichting en oxide thickness. Daarom, als stroom wordt gedetecteerd tijdens de proef, is het waarschijnlijk dat ten minste een van de oxidelagen wordt beschadigd en het apparaat moet worden weggegooid. Gewoonlijk minder dan 10% van de poorten lekkages vertonen. De opbrengst is bekend te worden beïnvloed door de vlakke verlenging van de poortelektroden. In het bijzonder, hoe groter de overlap van de poorten van de gate oxide gebied hoe waarschijnlijker het zal zijn om gate-naar-substraat lekkages hebben. Evenzo, hoe groter de overlapping tussen poorten van verschillende lagen hoe waarschijnlijker het optreden van gate-to-gate lekkage zijn. De vermelde opbrengst is relevant voor poorten die een gebied van ongeveer 50 urn 2 bezit op de dunne oxide en tussenlaag overlappingen van ongeveer 0,5 urn 2.

Zodra het apparaat de eerste lektest is verstreken, worden de bron en afvoer contacten verbonden aan een lock-in versterker en de poorten naar een modulair controleerbare-voltage batterij rack. In deze configuratie wordt het apparaat ingeschakeld on door wereldwijd ramping up van alle de poort spanningen tegelijk. Vervolgens wordt elke poortspanning afzonderlijk uitloopt terwijl de andere met hoge spanningen op het vermogen van individuele poorten knijpen actuele verifiëren. Figuur 4A toont representatieve sporen van deze metingen. De afwezigheid van ofwel een bron-drain geleiding route of individuele gate pinch-off is vaak een indicatie van een soort van de poort schade, zoals gate explosie of metalen discontinuïteit.

Tenslotte wordt het source-drain stroom gemeten als functie van source-drain vertekening en zuiger gate spanning aan de ondertekening van Coulomb blokkade 16 (zie figuur 4B) te observeren.

Metingen

Zodra een geschikte inrichting is gevonden, wordt deze verwijderd uit de vloeistof Hij vat, en gedroogd met een heteluchtpistool tot vorming van vocht, dat ESD kan veroorzaken. Tenslotte wordt overgebracht in een verdunning koelkast.

<p class = "jove_content"> De experimenten worden uitgevoerd in een self-made plastic verdunning koelkast met een basistemperatuur van ongeveer 100 mK. De cryostaat is in een vacuümkamer ondergedompeld in een 4,2 K helium bath. De elektrische leidingen gethermaliseerd op 1 K pot die ook wordt gebruikt om de binnenkomende 3He condenseren. In de mengkamer, de endotherme overgang van 3He atomen uit de 3He-rijke fase in de 3He-verdunde fase kan het systeem een basistemperatuur van ongeveer 100 mK bereiken.Zoals getoond in figuur 5, wordt de koelkast voorzien 20 dc lijnen en 3 rf lijnen gebruikt om de kamertemperatuur elektronica om het apparaat bij lage temperaturen. Vijf van de dc lijnen zijn Thermocoax kabels en 15 zijn twisted pair weefgetouw draden. Deze lijnen verbinden de poortelektroden van het monster om de batterij-aangedreven gelijkspanning bronnen. Spanningsdelers bij kamertemperatuur worden gebruikt om elektrische ruis op afzonderlijke gates verminderen. De RF-lijnen zijn halfstijf coax kabels die zijn verzwakt met 10 dB bij 4 K thermische ruis en dc geblokkeerd bij kamertemperatuur te verlagen. Deze lijnen zijn verbonden met de coplanaire golfgeleiders van de bias tees op de printplaat.

A low-noise transimpedantieversterker en een digitale multimeter gebruikt om de door de pomp stroom te meten. De elektronica is verbonden met het apparaat via batterijen optoisolators de vorming van aardlussen voorkomen. De RF besturingssignalen worden geproduceerd door een willekeurige golfvorm generator waarvan de aarding is geïsoleerd uit een van de cryostaat via een gelijkstroomcomponent blok (zie figuur 5).

De PCB bevat 16 pure dc lijnen en 4 vooroordeel tee lijnen gebruikt om dc en ac voltages te combineren bij lage temperatuur. Zoals getoond in figuur 3B, zijn RC discrete onderdelen waarmee de tee verbinding (R = 100 kQ, C = 10 nF) realiseren, en 50 Ω afgestemd geïntegreerde coplanaire golfgeleiders worden gebruikt voor de voortplanting van hoogfrequente signalen.

e_content "> Zodra het instrument zich op mK temperatuur, worden de gate spanning zodanig ingesteld dat één elektron bezetting in de QD bereikt. Vooral tunnel barrières worden gevormd onder gates BL en BR en een elektronen accumulatielaag geïnduceerd onder gates PL, SL en DL. Daartoe de slagboom spanningen beneden de inschakeltijd waarden, terwijl de accumulatie poorten zijn gepolariseerd in een groter-dan-turn-on voltage. Hierdoor wordt een QD wordt gevormd onder gate PL en de vlakke verlenging wordt via poort C1 en C2 waarvan de spanningen onder het inschakel waarden gehouden elektrostatische opsluiting te induceren. Vervolgens worden de RF signalen ingeschakeld periodiek moduleren de transparantie van de tunnelbarrière (s) en de elektrochemische potentiaal van de punt. Single-electron pompen wordt bereikt met één of twee sinusvormige aandrijfvoltages. Bij één signaalaandrijving, wordt het aandrijfsignaal toegevoerd aan de poort BL om het potentieel van de tunnelbarrière moduleren van de linker -kant vande QD. Bij de twee-signaalaandrijving, worden de ac excitaties toegepast gates BL en PL de potentialen van zowel het linker blok en de QD moduleren op dezelfde frequentie maar met verschillende fases en amplitudes. Deze extra vrijheidsgraden mogelijk maken om de richting van de elektronoverdracht 13 besturen. Een iteratief proces is meestal nodig om af te stemmen de belangrijkste experimentele parameters (dwz rf rijden signaalamplitudes / fasen en dc gate voltages) en het bereiken van optimale huidige quantisatie. Merk op dat geen van beide pompen protocollen heeft een drain-source voorspanning om de leiding doorverbinden. Derhalve worden de bron- en afvoerelektroden waaraan in de werking van de pomp. Figuur 6 toont de karakteristieke huidige plateaus op gehele veelvouden van ef verkregen door een twee-signaal sinusoïdale rit naar de ingang barrière (BL) en de plunjer (PL) poort. Deze gegevens worden genomen bij een relatief lage aandrijffrequentie (10 MHz) waarvoor het t Kanalen instellen van de parameters kan snel worden uitgevoerd. In de praktijk is het gewenst de pomp werken bij enkele honderden MHz, meestal vereist een veel fijnere parameteroptimalisatie 13.

Figuur 1. Microfabricage. (A) Schematische weergave van de belangrijkste stappen in microfabricage. Cartoons zijn niet op schaal getekend. (B) Realisatie van een gedoteerd gebied voor ohmse contacten. (C) Realisatie van gate oxide. (D) Metallisatie van ohmse contacten. (E) microscopische afbeelding van een afzonderlijk veld op een chip na de microfabricage is voltooid. Het gebied grootte is 1,2 x 1,2 mm 2. Klik hier om een grotere versie van deze figuur te bekijken.

Figuur 2. Nanofabrication. (A) Fabrication proces voor individuele gate lagen. Cartoons zijn niet op schaal getekend. (B) het 3-lagen gate nanostructuur voor lading pompen experimenten. Links: SEM beeld van een inrichting soortgelijk aan die wordt gebruikt voor de meting. Rechts:. Schematische dwarsdoorsneden van het toestel over X-cut en Y-cut Klik hier om een grotere versie van deze figuur te bekijken.

Figuur 3. Elektrische aansluitingen aan de steekproef. (A) lay-out van de printplaat. (B) Vergroting van een gebied van de PCB met een vooroordeel-tee (links) eend equivalent circuit (rechts). (C) Een chip met 6 afzonderlijke velden verlijmd op de chip houder en bond draden voor elektrische verbinding met de printplaat. (D) Microscopisch beeld van een individu veld na nanofabricage. (E) SEM beeld van de poort lay-out in het midden van de gate oxide regio. Klik hier om een grotere versie van deze figuur te bekijken.

Figuur 4. Voorlopige proeven. (A) bron-drain wisselstroom (root mean square) als functie van verschillende gate voltages. Sporen worden gemeten met een lock-in versterker met 50 mV RMS excitatie bij 113,17 Hz. Voor individuele poortspanning volgt de resterende gatespanning vastgesteld op 2,0 V, behalve V C1 = <em> V C2 = 0,0 V. (B) kleur kaart van source-drain stroom als funktie van plunjer poortspanning en de source-drain voorspanning. V SL = 1,5 V, V DL = 1,15 V, V BL = 0,78 V, V BR = 0,85 V, V C1 = V C2 = 0,0 V. Klik hier om een grotere versie van deze figuur te bekijken.

Figuur 5. Schematische voorstelling van de meetopstelling. Twintig dc lijnen (groen) en drie coaxiale rf lijnen (zwart) sluit de RT elektronica op de printplaat. De afvoer van de pomp (paarse) is verbonden met een transimpedantie versterker en een digitale multimeter via een optoisolator, terwijl de broncontact (rood) is geaard. Aparte aardverbindingen (indicated met verschillende symbolen) worden gebruikt voor de elektronische instrumentatie en de cryostaat elektrische leidingen. Klik hier om een grotere versie van deze figuur te bekijken.

Figuur 6. Voor kwantisering. Gepompte stroom als functie van V voor twee PL-sinusoïdale signalen drive f = 10 MHz toegepast gates BL en PL. Fase verschil = 49 graden, V RF PL = V RF BL = 0,31 V pp. De ideale positie van de pompen plateaus op integer veelvouden van ef worden weergegeven als rode horizontale lijnen. Klik hier om een grotere versie van deze figuur te bekijken.

Discussion

Het protocol beschreven in dit document beschreven technieken te fabriceren silicium MOS QDs, en de experimentele procedures hun functionele integriteit te testen en deze als één-electron pumps. Opmerkelijk door het afstemmen van de vormgeving poort hetzelfde fabricageproces wordt toegepast op inrichtingen die geschikt zijn voor quantum bits aflezing en controle 17, alsmede lading verpompen 12,13 produceren. We merken dat veel van de procesparameters in dit artikel aangegeven vermogen kan variëren afhankelijk van de fabricage gebruikte instrumenten (kalibratie, merk of model), alsook van het type siliciumsubstraat (dikte en achtergrond doping dichtheid). Hoeveelheden zoals blootstellingdosis lithografie of ontwikkelingstijd, ets of oxidatie duur, moeten zorgvuldig worden gekalibreerd en getest om een betrouwbare opbrengst te garanderen. Bovendien is het cruciaal om kruisbesmetting die voortvloeien uit het gebruik van dezelfde fabricage gereedschap voor verschillende processen te vermijden. Hiertoe een aantal critical stappen worden uitgevoerd met apparatuur uitgevoerd uitsluitend gewijd is aan silicium verwerking zoals metaal verdampers, zuurstof ovens en HF baden.

Meer in het algemeen wordt silicium die een groeiende interesse als het materiaal van keuze laadpompen 18-20 realiseren. Dit is mede te danken aan de aantrekkelijke perspectief van de implementatie van een nieuwe quantum gebaseerde elektrische stroom standaard met behulp van een industrie-compatibele silicium proces. Dit zou kunnen profiteren van gevestigde en betrouwbare integratie van technieken voor schaalbaarheid, parallellisatie en rijden overhead. Belangrijk is een volledig complementaire MOS (CMOS) technologie, los van traditionele metal als poortmateriaal, blijkt sterk verminderd achtergrond ladingsfluctuaties in één elektron inrichtingen 21. Zulke fluctuaties kunnen schadelijk zijn in het bereiken van metrologische nauwkeurigheid zijn.

Het protocol hier beschreven is beperkt tot het realiseren van MOS nano-inrichtingen met metalen hekken. Daarom, om achieve volledige industriële compatibiliteit en verminderen ladingsfluctuaties, zou het nodig zijn om de gate depositietechnieken te wijzigen en de sterk gedoteerde polykristallijne silicium als gate materiaal.

Tot slot hebben de MOS QD pompen hier besproken onlangs samen de technologische voorsprong van silicium met zeer goede prestaties in termen van accurate huidige generatie 13. Dit vloeit voort uit de hoge flexibiliteit van het ontwerp en fabricage werkwijze die mogelijk maken om meerdere gate lagen leidt tot een compact en veelzijdig systeem stapelen. De resulterende fijne tunability van de elektrostatische opsluiting van de stip met de potentie om achtergrond ladingsfluctuaties verminderen zet de te overwinnen de belangrijkste uitdagingen waargenomen in andere halfgeleiders pompen 22,23.

Disclosures

De auteurs hebben niets te onthullen.

Acknowledgments

Wij danken KY Tan, P. See en GC Tettamanzi voor nuttige discussies. Wij erkennen de financiële steun van de Australische Research Council (Grant No. DP120104710), de Academie van Finland (Grant No. 251.748, 135.794, 272.806) en steun van de Australische Nationale Fabrication Facility voor het apparaat fabricage. AR erkent financiële steun van de Universiteit van New South Wales Early Career Researcher Grant regeling. Het verstrekken van voorzieningen en technische ondersteuning door Aalto University in Micronova Nanofabrication Centre wordt ook erkend.

Materials

| Name | Company | Catalog Number | Comments |

| Silicon wafers | TOPSIL | 4 inch | |

| Electron-beam lithography machine | Raith gmbh | Raith 150two | |

| E-beam resist | MicroChem gmbh | PMMA | |

| Photoresist | MicroChem gmbh | nLOF2020 | |

| Mask aligner | Quintel | Q6000 | |

| Photoresist developer | MicroChem gmbh | AZ826MIF |

References

- Sze, S. M. Physics of Semiconductor Devices. , Wiley. Interscience, NY. 505-566 (1969).

- Moore, G. E. Cramming More Components onto Integrated Circuits. Electronics. 38, 114-117 (1965).

- Voisin, B., et al. Few-Electron Edge-State Quantum Dots in a Silicon Nanowire Field-Effect Transistor. Nano Lett. 14 (4), 2094-2098 (2014).

- Asenov, A., Brown, A. R., Davies, J. H., Savas, K., Slavcheva, G. Simulation of Instrinsic Parameter Fluctuations in Decananometer and Nanometer-Scale MOSFETs. IEEE Trans Electron Devices. 50 (9), 1837-1852 (2003).

- Zwanenburg, F. A., et al. Silicon Quantum Electronics. Rev. Mod. Phys. 85 (3), 961-1019 (2013).

- Ladd, T. D., et al. Quantum computers. Nature. 464 (7285), 45-53 (2010).

- Piquemal, F. Genevès, G. for a direct realization of the quantum metrological triangle. Metrologia. 37 (3), 207-211 (2000).

- Angus, S. J., Ferguson, A. J., Dzurak, A. S., Clark, R. G. Gate-Defined Quantum Dots in Intrinsic Silicon. Nano Lett. 7 (7), 2051-2055 (2007).

- Gonzalez-Zalba, M. F., Heiss, D., Podd, G., Ferguson, A. J. Tunable aluminium-gated single electron transistor on a doped silicon-on-insulator etched nanowire. Appl. Phys. Lett. 101 (10), 103504-103501 (2014).

- Lim, W. H., et al. Observation of the single-electron regime in a highly tunable silicon quantum dot. Appl. Phys. Lett. 95 (24), 242102-242103 (2009).

- Yang, C. H., et al. Spin-valley lifetimes in silicon quantum dots with tunable valley splitting. Nat. Commun. 4 (2069), (2013).

- Chan, K. W., et al. Single-electron shuttle based on a silicon quantum dot. Appl. Phys. Lett. 98 (21), 212103-212101 (2011).

- Rossi, A., et al. An accurate single-electron pump based on a highly tunable silicon quantum dot. Nano Lett. 14 (6), 3405-3411 (2014).

- Pekola, J. P., et al. Single-electron current sources: Toward a refined definition of the ampere. Rev. Mod. Phys. 85 (4), 1421-1472 (2013).

- Giblin, S. P., et al. Towards a quantum representation of the ampere using single electron pumps. Nat. Commun. 3, 930 (2012).

- Kouwenhoven, L. P., Austing, D. G., Tarucha, S. Few-electron quantum dots. Rep. Prog. Phys. 64 (6), 701-736 (2001).

- Veldhorst, M., et al. An addressable quantum dot qubit with fault-tolerant control fidelity. Nat. Nanotech. 9 (12), 981-985 (2014).

- Fujiwara, A., Nishiguchi, K., Ono, Y. Nanoampere charge pump by single-electron ratchet using silicon nanowire metal-oxide-semiconductor field-effect transistor. Appl. Phys. Lett. 92 (4), 042102-1-042102-3 (2008).

- Jehl, X., et al. Hybrid Metal-Semiconductor Electron Pump for Quantum Metrology. Phys. Rev. X. 3 (2), 021012-1-021012-7 (2013).

- Tettamanzi, G. C., Wacquez, R., Rogge, S. Charge pumping through a single donor atom. New J. Phys. 16 (6), 063036-1-063036-17 (2014).

- Koppinen, P. J., Stewart, M. D., Zimmerman, N. M. Fabrication and Electrical Characterization of Fully CMOS-Compatible Si Single-Electron Devices. IEEE Trans Electron Devices. 60 (1), 78-83 (2013).

- Fletcher, J. D., et al. Stabilization of single-electron pumps by high magnetic fields. Phys. Rev. B. 86 (15), 155311-1-155311-6 (2012).

- Kataoka, M., et al. Tunable Nonadiabatic Excitation in a Single-Electron Quantum Dot. Phys. Rev. Lett. 106 (12), 126801-1-126801-4 (2011).