Protocol

Remarque: Ce protocole décrit les procédures utilisées pour fabriquer, emballer et tester des pompes à électron unique à base de silicium technologie MOS QD. Les étapes décrites dans les sous-sections 1 et 2 sont effectuées dans une salle blanche de ISO5, tandis que ceux de l'article 3 sont effectuées dans les laboratoires de ISO6. Les conditions ambiantes sont contrôlées en permanence. Les valeurs nominales de température et d'humidité sont fixées à 20 ± 1 ° C et 55% ± 5%, respectivement.

1. microfabrication

- Champ Oxide

- Nettoyer la plaquette par immersion dans ce qui suit: gravure de piranha (10 min), désionisée (DI) de l'eau (10 min), RCA-deux solutions (DI eau 175 ml, HCl 30 ml, H 2 O 2 30 ml à 100 ° C pendant 10 min), de l'eau désionisée (5 min), fluorhydrique (HF) de l'acide dilué dans l'eau 10: 1 (10 sec), de l'eau déminéralisée (10 min). Utilisez des vêtements de protection lors de la manipulation HF (à savoir, lunettes, tablier PVC, et des gants en PVC). Procédez dans l'ordre indiqué.

- Placer la plaquettedans le four d'oxydation à 900 ° C et d'oxyder dans les étapes comme suit: O 2 sec (10 min), O 2 humide (40 min), O 2 sec (10 min), N 2 (15 min).

- Contacts ohmiques

- Effectuer photolithographie et gravure de l'oxyde.

- Déposer une couche de promoteur d'adhérence hexaméthyldisilazane (HMDS) quelques nm d'épaisseur sur la surface de la plaquette comme suit: pré-cuire sur une plaque chauffante à 110 ° C pendant 1 min, versez ~ 50 ml de HMDS dans un récipient en verre, placer le bécher et la plaquette dans la chambre à vide, évacuer et d'attendre 2 min.

- Spin une couche 2-4 um d'épaisseur de résine photosensible à la fois sur le dos et les côtés avant de la tranche (3000-5000 rpm, 25-40 sec selon l'épaisseur souhaitée).

- Exposer à la lumière ultra-violette d'alignement de masque (10 mW / cm 2 pour 4-10 sec selon résister épaisseur). Post-cuisson sur une plaque chauffante à 110 ° C pendant 1 min.

- Développer pour 1-2 minutes, puis rincer à l'eau déminéralisée. Effectuer gravure plasma O 2 pendant 20 min (pression = 340 mTorr, puissance incidente = 50 W; la puissance réfléchie <1 W).

- Oxyde gravure dans une solution d'acide HF tamponnée (15: 1, 4-5 min, gravure 20 nm / min de la vitesse à 30 ° C). Rincer à l'eau déminéralisée (5 min). Sécher avec N 2.

- Retirer le photorésist par immersion dans de l'acétone. Rincer à l'isopropanol (IPA), puis sécher avec N 2.

- Passer plaquette dans un four à 1000 ° C avec une source de phosphore (N 2 flux de 30 à 45 min en fonction de la densité de dopage désiré).

- Enlever la couche d'oxyde contaminée avec de l'acide HF dilué dans l'eau (10: 1, 3-4 min, 40 nm / min de la vitesse de gravure à 30 ° C), rincer à l'eau déminéralisée (10 min).

- Oxyder comme dans 1.1.2.

- Effectuer photolithographie et gravure de l'oxyde.

- Oxyde de grille

- Répétez les étapes 1.2.1 et 1.2.2.

- Placez plaquette dans un four dédié à 800 ° C et d'oxyder dans les étapes comme suit: O 2 sec (10 min), dichloroethylene + O 2 (20 min), O 2 sec (10 à 30 min en fonction de l'épaisseur désirée d'oxyde), N 2 (15 min).

- Contacts ohmiques métallisation

- Répétez l'étape 1.2.1.

- Placez plaquette dans l'évaporateur à faisceau d'électrons. Évaporer 100 nm de l'aluminium à 0,2-0,5 nm / s et 5 x 10 -6 Torr.

- Faire tremper la plaquette en N-méthyl-2-pyrrolidone (NMP) sur plaque chauffante à 80 ° C pendant 1 heure pour enlever le métal. Utilisez agitation ultrasonique si nécessaire. Rincer à l'IPA pendant 2 min. Sécher avec N 2.

- Recuit dans la formation de gaz à 400 ° C pendant au moins 15 min.

2. nanofabrication

- Wafer Dicing

- Spin toute résister sur la plaquette d'agir comme revêtement de protection (type de paramètres de polymères et de filage ne sont pas pertinentes à ce stade).

- Utilisez diamant pointe dicer pour couper la tranche en puces individuelles de ~ 10 x 2 mm 2.

- Nettoyage

- Faire tremper dans la NMP pendant 1 heure sur plaque chauffante à 80 ° C, puis rincer dans de l'IPA pendant 2 min. Sécher avec N 2.

- Effectuer gravure plasma O 2 pendant 5 min (puissance incidente = 50 W; la puissance réfléchie <1 W).

- Spin propre avec de l'acétone et de l'IPA (7500 rpm, 30 sec)

- marqueurs d'alignement de motifs

- Spin polyméthacrylate de méthyle (PMMA 950k) A4 résist (5,000-7,500 rpm, 30 secondes en fonction de l'épaisseur souhaitée). Épaisseur de travail typique ≈ 150-200 nm. Cuire la résine sur une plaque chauffante à 180 ° C pendant 90 sec.

- Effectuer la lithographie par faisceau d'électrons. Utiliser les conditions d'écriture suivantes: l'énergie du faisceau = 30 keV, courant de faisceau de 30 pA, dose de zone ≈ 500-650 uC / cm 2 en fonction de la taille des marqueurs et de résister à l'épaisseur.

- Développer le résister dans une solution de méthylisobutylcétone et de l'IPA (1: 3) pour 40-60 sec, puis rincer dans de l'IPA pendant 20 sec. Sécher avec N 2 pistolet.

- Endroitla puce dans l'évaporateur à faisceau d'électrons. Évaporer 15 nm de Ti et 65 nm de Pt à 0,2-0,4 nm / s et 5 x 10 -6 Torr.

- Soulevez le métal comme à l'étape 1.4.3.

- Clean puce comme dans les étapes 2.2.2-2.2.3.

- Porte motifs

- Spin résister en 2.3.1.

- Effectuer la lithographie par faisceau d'électrons. Utiliser les conditions d'écriture suivantes pour les fonctions à haute résolution: l'énergie du faisceau = 30 keV, courant de faisceau de 30 pA, dose de zone ≈ 500-700 uC / cm 2. Ecrire conditions pour les fonctions à faible résolution: l'énergie du faisceau = 15 keV, courant de faisceau de 10 nA, dose de zone ≈ 400-600 uC / cm 2.

- Développer la réserve comme dans 2.3.3.

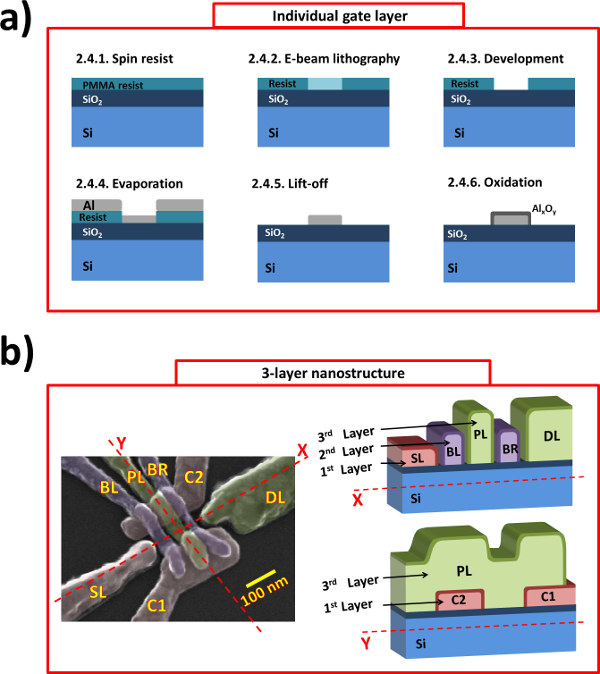

- Placez la puce dans l'évaporateur thermique. Al s'évaporer à 0,1-0,4 nm / s et 1-9 x 10 -6 mbar. l'épaisseur de la cible varie en fonction du nombre de couches, comme représenté sur la figure 2B (25-35 nm pour la couche 1, de 45 à 65 nm pour la couche 2, de 75 à 90 nm pour Layer 3).

- Soulevez le métal comme à l'étape 1.4.3.

- Effectuer Al oxydation sur une plaque de cuisson à 150 ° C pendant 5-10 min.

- Clean puce à l'étape 2.2.3.

- Répétez les étapes 2.4.1-2.4.7 deux fois pour réaliser le 3-couche empilement de grille.

3. Dispositif d'emballage

- Chip Dice comme dans l'étape 2.1

- Rincer les petites puces dans de l'acétone et de l'IPA résultant pendant 2 minutes.

- Collez un morceau individuel à une carte de circuit imprimé (PCB) avec le PMMA A5. Attendre 2 min pour sécher. Sinon, pour améliorer la thermalisation, utilisez époxy d'argent.

- Chargez le PCB sur une colle de coin et de procéder au câblage.

4. Dispositif tests d'intégrité

- Montez le PCB contenant le dispositif câblé sur une sonde d'immersion.

- Câbler les lignes électriques du PCB à ceux de la sonde d'immersion.

- Insérez la sonde dans un récipient contenant de l'hélium liquide. Procéder lentement pour éviter excessive hélium bhuile-off.

- Pour chaque porte de l'appareil, connectez l'électrode à température ambiante correspondante de la sonde à une unité source de mesure, tout en gardant les autres portes à la terre. Régler le courant de la conformité à quelques nA. Balayer la tension de zéro à 1,5 V par pas de 0,1 V, mesurer et enregistrer le courant.

- Connecter chaque ligne de grille à une source de tension continue variable de batterie, la ligne de source pour le haut-source de tension en courant alternatif d'un amplificateur lock-in, et la conduite d'évacuation à l'orifice de l'amplificateur à verrouillage d'entrée.

- Mesurer la source-drain conductance pour différentes configurations de tension de grille (voir Figure 4).

- Globalement rampe jusqu'à les tensions appliquées aux portes BL, BR, PL, SL et DL, en gardant C1 et C2 portes à la terre. Notez les caractéristiques de l'appareil «Turn-sur».

- Individuellement rampe en bas de chaque tension de grille et enregistrer les caractéristiques de pinch-off 'les portes.

- Régler les tensions de grille pour définir électrostatique d'un qudot antum en réglant les tensions sur BL et BR (PL, SL et DL) plus petit (plus) que le turn-on tensions. Enregistrer les caractéristiques de blocage de Coulomb.

Representative Results

Fabrication de périphériques

Le processus de microfabrication initial (sous-section 1 du Protocole) est effectuée sur un 4-pouces haute pureté plaquette de silicium commerciale (de type n 10 12 cm -3 ≈ concentration de dopage; résistivité> 10 kΩcm; épaisseur = 310-340 um ). L'objectif est de réaliser le substrat sur lequel les électrodes de grille seront déposés. Ce substrat est constitué d'une région intrinsèque coiffé avec de l'oxyde de champ (étape 1.1), une région n + coiffé avec de l'oxyde de champ (étape 1.2), une région intrinsèque coiffé de haute qualité de l'oxyde de grille (étape 1.3), et un métallisée région n + pour contacts ohmiques (étape 1.4). Figures 1A-D illustrent les principales étapes du processus de microfabrication. Figure 1E montre une image microscopique d'un champ de substrat après microfabrication. La taille minimum pour la lithographie à ce stade est d'environ 4 um.

Le SiO2 la couche d'oxyde développée à l'étape 1.1 a une épaisseur nominale de 100 nm, et est utilisé en tant que couche de passivation. Les régions de type n qui agissent comme des conducteurs ohmiques sont obtenus par diffusion de phosphore. La densité cible de dopage est d'environ 19 octobre au 20 octobre cm -3. La haute qualité de SiO 2 qui est cultivé de manière sélective pour être utilisés comme diélectrique de grille a une épaisseur nominale de 5 nm. La densité de défauts d'interface cible est <10 10 cm -2 eV -1 à mi-écart. Un four à triple mur dédié et délibérément construit est utilisé pour ce processus. Ce système est conçu pour réduire au minimum la contamination par des ions de métaux lourds et des ions de métaux alcalins mobiles, ainsi que d'empêcher l'humidité de se diffuser dans la chambre d'oxydation. Afin de former des contacts électriques, plaquettes d'aluminium sont déposées par évaporation par faisceau d'électrons sur une partie des régions de type n.

Le processus de nanofabrication (voir la sous-section 2) est réalisée sur la puce substrAtes obtenus en découpant la plaquette traitée à l'étape 1. Le but est de réaliser les électrodes de grille à l'échelle nanométrique utilisés pour définir les électrostatique QDs MOS. Chaque terme de nanofabrication produit typiquement 10-15 échantillons de dispositifs complets. micrographie électronique à balayage (MEB) de formation d'image de 2/1 dispositifs par lot est habituellement effectuée pour confirmer que les étapes de lithographie EBL ont été couronnés de succès. Depuis imagerie SEM peut injecter des charges dans le substrat ou dans les portes métalliques et causer des fuites, seul un petit nombre de dispositifs est vérifiée de cette manière, alors que le reste est testé électriquement. Taille minimum pour la lithographie à ce stade est d'environ 35 nm. Pour obtenir une bonne uniformité des films déposés Al, le métal est évaporé à des taux plus lent que quelques angströms / seconde, tandis que le substrat est monté sur une platine tournante. Cet article est maintenu à la température ambiante, et la taille des grains d'Al est estimé à environ 20 nm. La figure 2A illustre les principales étapes de la nanofabricatioProcédé de n. La figure 2B montre une image MEB avec laquelle la définition correcte des électrodes de grille est vérifiée. En général, on vise à la réalisation de ces portes qui définissent directement le QD (BL, BR et PL) avec la plus petite taille possible de fonctionnalité. En revanche, ces portes utilisées pour définir les réservoirs d'électrons (DL et SL) peuvent avoir de plus grandes dimensions pour éviter la discrétisation involontaire de niveaux d'énergie dans les fils. Les nano-échelle marqueurs Ti / Pt réalisés à l'étape 2.3 sont utilisés comme référence pour un alignement constant des trois couches de portes. Le platine est choisi pour son excellent contraste par rapport à la surface de SiO 2 dans le faisceau d'électrons. Le titane est utilisé pour améliorer l'adhérence.

À toutes les étapes du processus de fabrication, une pince à épiler en fibre de carbone-pointe sont utilisées pour gérer les puces, afin de réduire le risque de décharge électrostatique destructrice (ESD).

Enfin, afin d'effectuer des mesures électriques sur individeux dispositifs, chaque puce doit être clivé en petits morceaux d'environ 2 x 2 mm 2 (sous-section 3). Chaque morceau est ensuite collée sur un circuit imprimé sur mesure (Rogers R03010 faible perte diélectrique) dont les broches sont reliées aux électrodes de dispositif par des fils al. Fil de liaison est réalisée avec une machine de colle en forme de coin sans chauffer les copeaux. Le choix des paramètres appropriés de liaison repose sur deux considérations. D'une part, la liaison fil doit perforer le Al y O x couche thermique et un bon contact métal-métal avec le plot de grille. D'autre part, une contrainte mécanique excessive peut conduire à un événement de punch-creux qui endommage le d'oxyde de champ sous les portes et causer des fuites de substrat. Au cours du processus de câblage, l'utilisation d'un bracelet antistatique est conseillé d'éviter les décharges électrostatiques. Dans la figure 3, une puce avec 6 appareils individuels est collé sur le PCB.

des tests d'intégrité de l'appareil

Before chargement d'un dispositif dans un mK température plateforme de mesure comme un réfrigérateur à dilution, tests électriques préliminaires sont réalisées à 4,2 K pour vérifier l'intégrité de l'échantillon (voir la sous-section 4 du Protocole). A cet effet, le circuit imprimé est inséré dans une enceinte de cuivre exempt d'oxygène et est monté sur une sonde d'immersion, qui est immergé dans le liquide éventuellement He.

Le test initial est généralement un test de fuite qui est effectué séquentiellement sur chaque porte. Une unité de source-mesure est reliée à une électrode de grille individuelles tandis que les autres sont à la masse. La tension est en rampe jusqu'à 1,5 V et le courant est mesuré à la source. Dans cette gamme de tension, une porte fonctionne correctement est pas censé mener, parce que la couche de SiO 2 isole le métal du substrat de silicium et Al y O x isole portes se chevauchent. Typiquement, claquage de l'oxyde est connu pour se produire pour des tensions plus grandes que ~ 4 V, en fonction de la géométrie de l'appareil et de l'oxyde thickness. Par conséquent, si le courant est détecté au cours de l'essai, il est probable qu'au moins une des couches d'oxyde est endommagé et le dispositif doit être mis au rebut. Habituellement, moins de 10% des grilles correspond à des fuites. Le rendement est connu pour être affecté par l'extension plane des électrodes de grille. En particulier, plus le chevauchement des portes avec la région d'oxyde de grille plus il sera d'avoir des fuites porte-à-substrat. De même, plus le chevauchement entre les portes de différentes couches plus l'occurrence de fuites porte-à-porte sera. Le rendement indiqué est pertinente pour les portes qui occupent une superficie d'environ 50 um 2 sur l'oxyde mince et avec intercalaire chevauche d'environ 0,5 um 2.

Une fois que l'appareil a passé le test de fuite initiale, les contacts de source et de drain sont connectés à un amplificateur lock-in et les portes à un rack de la batterie contrôlable tension modulaire. Dans cette configuration, l'appareil est allumé on la montée en cadence globalement toutes les tensions de grille simultanément. Ensuite, chaque tension de grille est séparée en rampe vers le bas tout en conservant les autres à haute tension pour vérifier la capacité des portes individuelles à pincer le courant. La figure 4A montre des traces représentatives de ces mesures. L'absence d'une voie de conduction source-drain ou un portail individuel pincement est souvent une indication d'un certain type de dommages de porte comme porte explosion ou discontinuité de métal.

Enfin, le courant source-drain est mesurée en fonction de partialité source-drain et la tension de grille de piston pour observer la signature de blocage de Coulomb 16 (voir la figure 4B).

Mesures

Une fois que le dispositif approprié a été trouvé, il est retiré de la cuve, il liquide, et on le sèche avec un pistolet à air chaud pour éviter la formation d'humidité qui peut provoquer des décharges électrostatiques. Enfin, il est transféré dans un réfrigérateur à dilution.

<p class = "jove_content"> Les expériences sont effectuées dans une dilution en plastique réfrigérateur self-made avec une température de base d'environ 100 mK. Le cryostat se trouve dans une chambre à vide immergé dans un bain d'hélium K 4,2. Les lignes électriques sont thermalisés au pot 1 K, qui est également utilisé pour condenser la vapeur entrant 3He. Dans la chambre de mélange, le transfert endothermique d'atomes 3He de la phase 3He riche dans la phase 3He-diluée permet au système d'atteindre une température de base d'environ 100 mK.Comme le montre la Figure 5, le réfrigérateur est équipé de 20 lignes à courant continu et trois lignes de rf utilisés pour connecter les composants électroniques à température ambiante sur l'appareil à basse température. Cinq des lignes à courant continu sont des câbles THERMOCOAX et 15 sont torsadés des fils de paires de métiers à tisser. Ces lignes relient les électrodes de l'échantillon à des sources de tension à courant continu alimentés par batterie grille. diviseurs de tension à la température ambiante sont utilisés pour réduire le bruit électrique sur les portes individuelles. Les lignes de RF sont des câbles coaxiaux semi-rigides qui sont atténué de 10 dB à 4 K pour réduire le bruit thermique et dc bloqué à RT. Ces lignes sont connectées aux guides d'ondes coplanaires des tés de polarisation sur le circuit imprimé.

Un faible bruit amplificateur à transimpédance et un multimètre numérique sont utilisés pour mesurer le courant généré par la pompe. Le système électronique est relié au dispositif par l'intermédiaire d'optocoupleurs alimentés par batterie pour empêcher la formation de boucles de masse. Les signaux d'excitation RF sont produits par un générateur de forme d'onde arbitraire dont la masse est isolée de celle du cryostat par l'intermédiaire d'un bloc de composant à courant continu (voir figure 5).

Le PCB contient 16 lignes continues pures et 4 polarisation tee lignes utilisées pour combiner tension continue et alternative à basse température. Comme le montre la figure 3B, RC composants discrets sont utilisés pour réaliser le raccord en T (R = 100 kQ, C = 10 nF), et 50 Ω appariés guides d'ondes coplanaires intégrées sont utilisées pour la propagation des signaux à haute fréquence.

e_content "> Une fois que le dispositif est à la température mK, les tensions de grille sont ajustés de sorte que l'occupation à électron unique dans la QD est atteint. En particulier, les barrières tunnel sont formées sous les portes BL et BR, et une couche d'accumulation d'électrons est induite sous portes PL, SL et DL. À cette fin, les tensions de grille de barrière sont définies ci-dessous leur tour sur des valeurs, alors que les portes d'accumulation sont polarisés à un supérieur à la tension d'allumage. De cette façon, un QD est formé sous la grille PL et son extension plane est commandé par des portes C1 et C2 dont les tensions sont maintenues au-dessous de leur mise en fonction des valeurs d'induire confinement électrostatique. Ensuite, les signaux RF sont mis sous tension pour moduler périodiquement la transparence de la barrière (s) à effet tunnel, et la électrochimique le potentiel du point. pompage à l'unité d'électrons est réalisé avec une ou deux tensions de commande sinusoïdales. Dans le cas de l'entraînement d'un signal, le signal de commande est appliqué à la porte BL à moduler le potentiel de la barrière à effet tunnel à la gauche -côté deQD. Dans le cas de l'entraînement de deux signaux, les excitations à courant alternatif sont appliqués à des grilles PL BL et pour moduler les potentiels à la fois de la gauche et la barrière QD à la même fréquence mais avec des phases et amplitudes. Ces degrés de liberté supplémentaires permettent de contrôler la direction du transfert d'électrons 13. Un processus itératif est généralement nécessaire de régler les principaux paramètres expérimentaux (par exemple, les amplitudes de signal d'attaque à haute fréquence / phase et des tensions de grille en courant continu) et à réaliser une quantification optimale de courant. Remarquez qu'aucun des deux protocoles de pompage a besoin d'un biais drain-source pour effectuer des transferts de charge. Par conséquent, les électrodes source et drain sont mis à la terre pendant le fonctionnement de la pompe. La figure 6 montre les plateaux courant caractéristique à des multiples entiers de l'ef obtenues en appliquant un deuxième signal d'entraînement sinusoïdale à la barrière d'entrée (BL) et le plongeur (PL) de grille. Ces données sont prélevés à une fréquence d'excitation relativement faible (10 MHz) pour laquelle la t Downloaded from www.vandenborre.be Régler des paramètres peut être effectuée rapidement. Dans la pratique, il est souhaitable de faire fonctionner la pompe à plusieurs centaines de MHz, ce qui nécessite généralement un paramètre d'optimisation beaucoup plus fine 13.

Figure 1. microfabrication. (A) Représentation schématique des principales étapes de microfabrication. Les dessins animés ne sont pas dessinés à l'échelle. (B) Réalisation d'une région dopée pour les contacts ohmiques. (C) Réalisation d'oxyde de grille. (D) métallisation des contacts ohmiques. (E) l'image microscopique d'un champ individuel sur une puce après le procédé de microfabrication est terminée. Taille du champ est de 1,2 x 1,2 mm 2. S'il vous plaît cliquez ici pour voir une version plus grande de cette figure.

Figure 2. nanofabrication. (A) Procédé de fabrication de couches de grille individuels. Les dessins animés ne sont pas dessinés à l'échelle. (B) Le 3-couche porte nanostructure utilisés pour des expériences responsable de pompage. A gauche: image MEB d'un dispositif similaire à celui utilisé pour les mesures. Droite:. Vues en coupe schématique du dispositif à travers coupe X et Y-cut S'il vous plaît cliquez ici pour voir une version plus grande de cette figure.

Figure 3. Connexions électriques à l'échantillon. (A) Disposition de la carte de circuit imprimé. (B) Le grossissement d'une région de la carte électronique avec une polarisation en T (à gauche) uncircuit équivalent d (à droite). (C) Une puce avec 6 champs individuels collées sur le support de la puce et des fils de connexion pour le raccordement électrique au PCB. (D) d'image microscopique d'un champ individuel après nanofabrication. L'image (E) SEM de la disposition de la porte au centre de la région d'oxyde de grille. S'il vous plaît, cliquez ici pour voir une version plus grande de cette figure.

Figure 4. Des tests préliminaires. (A) de courant source-drain ac (Root Mean Square) en fonction de différentes tensions de grille. Traces sont mesurées avec un amplificateur lock-in avec 50 mV RMS excitation à 113.17 Hz. Pour individu tension de grille retrace les tensions de grille restants sont fixés à 2,0 V, à l'exception de V C1 = <em> V C2 = 0,0 V. (B) Carte couleur du courant source-drain en fonction de plongeur tension de grille et de source-drain la tension de polarisation. V SL = 1,5 V, V DL = 1,15 V, V BL = 0,78 V, V BR = 0,85 V, V = V C1 C2 = 0.0 V. S'il vous plaît cliquez ici pour voir une version plus grande de cette figure.

Figure 5. Schéma lignes de la mesure mise en place. Vingt cc (vert) et trois lignes coaxiaux RF (noir) relient l'électronique RT sur le PCB. Le drain de la pompe (pourpre) est connecté à un amplificateur à transimpédance et à un multimètre numérique par l'intermédiaire d'un opto-isolateur, tandis que le contact de source (rouge) est mis à la terre. Prises de terre distinctes (indicated avec des symboles différents) sont utilisés pour l'instrumentation électronique et les lignes électriques cryostat. S'il vous plaît, cliquez ici pour voir une version plus grande de cette figure.

Figure 6. quantification actuel. Pumped courant en fonction de V PL pour deux signaux d'entraînement sinusoïdal à f = 10 MHz appliqué aux portes BL et PL. Différence de phase = 49 °, V = V RF PL BL RF = 0,31 V pp. La position idéale des plateaux de pompage à des multiples entiers de ef sont indiqués par des lignes horizontales rouges. S'il vous plaît cliquez ici pour voir une version plus grande de cette figure.

Discussion

Le protocole indiqué dans le présent document décrit les techniques pour fabriquer du silicium MOS QDs, ainsi que les procédures expérimentales pour tester leur intégrité fonctionnelle et les gérer comme des pompes à électron unique. Remarquablement, en adaptant la conception de grille, le même processus de fabrication peut être utilisé pour produire des dispositifs appropriés pour la lecture de bit quantique et de contrôle 17, ainsi que de pompage de charge 12,13. Nous notons que la plupart des paramètres du processus cités dans cet article peuvent varier selon les outils de fabrication utilisés (étalonnage, marque ou le modèle), ainsi que sur le type de substrat de silicium (épaisseur et la densité de dopage de fond). Des quantités telles que la dose d'exposition de lithographie ou de temps de développement, de gravure ou de la durée d'oxydation, doivent être soigneusement calibrés et testés pour assurer un rendement fiable. En outre, il est essentiel d'éviter la contamination croisée résultant de l'utilisation des mêmes outils de fabrication des différents processus. A cette fin, un certain nombre de critical étapes sont effectuées avec du matériel exclusivement dédiée au traitement de silicium tels que des évaporateurs de métaux, des fours à oxygène et des bains de HF.

Plus généralement, le silicium attire un intérêt croissant en tant que matériau de choix pour réaliser des pompes de charge 18-20. Ceci est partiellement dû à la perspective attrayante de mettre en œuvre une nouvelle norme de courant électrique basé quantique en utilisant un procédé de silicium industrie compatible. Cela bénéficier de techniques d'intégration bien établies et fiables pour l'évolutivité, la parallélisation et les frais généraux de conduite. Surtout, un MOS complémentaire (CMOS) complet, dépourvu de métal traditionnel comme le matériau de grille, a montré fortement réduits fond fluctuations de charge dans les dispositifs à électron unique 21. Ces fluctuations peuvent être nocifs pour atteindre une précision métrologique.

Le protocole décrit ici est limitée à la réalisation de nano-dispositifs MOS avec des portes en métal. Par conséquent, pour Achieve compatibilité industrielle complète et à réduire les fluctuations de charge, il serait nécessaire de modifier les techniques de dépôt de grille et utiliser du silicium polycristallin fortement dopé que le matériau de grille.

En conclusion, les pompes MOS QD discutés ici ont récemment combiné l'avantage technologique de silicium avec de très bonnes performances en termes de génération actuelle précise 13. Cette situation découle de la grande flexibilité du processus de conception et de fabrication qui permettent d'empiler plusieurs couches de grille menant à un système compact et polyvalent. L'accordabilité amende résultant du confinement électrostatique de la dot avec le potentiel de réduire les fluctuations de charge fond ouvre la voie pour surmonter les principaux défis observés dans d'autres semi-conducteurs pompes 22,23.

Disclosures

Les auteurs ont rien à révéler.

Acknowledgments

Nous remercions KY Tan, P.-Siège et GC Tettamanzi pour des discussions utiles. Nous reconnaissons l'appui financier du Conseil australien de la recherche (subvention n ° DP120104710), l'Académie de Finlande (Grant No. 251748, 135794, 272806) et le soutien de l'installation de fabrication nationale australienne pour la fabrication de dispositifs. AR reconnaît le soutien financier du régime de subvention du chercheur de l'Université de New South Wales en début de carrière. La fourniture d'installations et de soutien technique par l'Université Aalto à Micronova Centre nanofabrication est également reconnu.

Materials

| Name | Company | Catalog Number | Comments |

| Silicon wafers | TOPSIL | 4 inch | |

| Electron-beam lithography machine | Raith gmbh | Raith 150two | |

| E-beam resist | MicroChem gmbh | PMMA | |

| Photoresist | MicroChem gmbh | nLOF2020 | |

| Mask aligner | Quintel | Q6000 | |

| Photoresist developer | MicroChem gmbh | AZ826MIF |

References

- Sze, S. M. Physics of Semiconductor Devices. , Wiley. Interscience, NY. 505-566 (1969).

- Moore, G. E. Cramming More Components onto Integrated Circuits. Electronics. 38, 114-117 (1965).

- Voisin, B., et al. Few-Electron Edge-State Quantum Dots in a Silicon Nanowire Field-Effect Transistor. Nano Lett. 14 (4), 2094-2098 (2014).

- Asenov, A., Brown, A. R., Davies, J. H., Savas, K., Slavcheva, G. Simulation of Instrinsic Parameter Fluctuations in Decananometer and Nanometer-Scale MOSFETs. IEEE Trans Electron Devices. 50 (9), 1837-1852 (2003).

- Zwanenburg, F. A., et al. Silicon Quantum Electronics. Rev. Mod. Phys. 85 (3), 961-1019 (2013).

- Ladd, T. D., et al. Quantum computers. Nature. 464 (7285), 45-53 (2010).

- Piquemal, F. Genevès, G. for a direct realization of the quantum metrological triangle. Metrologia. 37 (3), 207-211 (2000).

- Angus, S. J., Ferguson, A. J., Dzurak, A. S., Clark, R. G. Gate-Defined Quantum Dots in Intrinsic Silicon. Nano Lett. 7 (7), 2051-2055 (2007).

- Gonzalez-Zalba, M. F., Heiss, D., Podd, G., Ferguson, A. J. Tunable aluminium-gated single electron transistor on a doped silicon-on-insulator etched nanowire. Appl. Phys. Lett. 101 (10), 103504-103501 (2014).

- Lim, W. H., et al. Observation of the single-electron regime in a highly tunable silicon quantum dot. Appl. Phys. Lett. 95 (24), 242102-242103 (2009).

- Yang, C. H., et al. Spin-valley lifetimes in silicon quantum dots with tunable valley splitting. Nat. Commun. 4 (2069), (2013).

- Chan, K. W., et al. Single-electron shuttle based on a silicon quantum dot. Appl. Phys. Lett. 98 (21), 212103-212101 (2011).

- Rossi, A., et al. An accurate single-electron pump based on a highly tunable silicon quantum dot. Nano Lett. 14 (6), 3405-3411 (2014).

- Pekola, J. P., et al. Single-electron current sources: Toward a refined definition of the ampere. Rev. Mod. Phys. 85 (4), 1421-1472 (2013).

- Giblin, S. P., et al. Towards a quantum representation of the ampere using single electron pumps. Nat. Commun. 3, 930 (2012).

- Kouwenhoven, L. P., Austing, D. G., Tarucha, S. Few-electron quantum dots. Rep. Prog. Phys. 64 (6), 701-736 (2001).

- Veldhorst, M., et al. An addressable quantum dot qubit with fault-tolerant control fidelity. Nat. Nanotech. 9 (12), 981-985 (2014).

- Fujiwara, A., Nishiguchi, K., Ono, Y. Nanoampere charge pump by single-electron ratchet using silicon nanowire metal-oxide-semiconductor field-effect transistor. Appl. Phys. Lett. 92 (4), 042102-1-042102-3 (2008).

- Jehl, X., et al. Hybrid Metal-Semiconductor Electron Pump for Quantum Metrology. Phys. Rev. X. 3 (2), 021012-1-021012-7 (2013).

- Tettamanzi, G. C., Wacquez, R., Rogge, S. Charge pumping through a single donor atom. New J. Phys. 16 (6), 063036-1-063036-17 (2014).

- Koppinen, P. J., Stewart, M. D., Zimmerman, N. M. Fabrication and Electrical Characterization of Fully CMOS-Compatible Si Single-Electron Devices. IEEE Trans Electron Devices. 60 (1), 78-83 (2013).

- Fletcher, J. D., et al. Stabilization of single-electron pumps by high magnetic fields. Phys. Rev. B. 86 (15), 155311-1-155311-6 (2012).

- Kataoka, M., et al. Tunable Nonadiabatic Excitation in a Single-Electron Quantum Dot. Phys. Rev. Lett. 106 (12), 126801-1-126801-4 (2011).