Protocol

注:このプロトコルは、製造、パッケージとシリコンMOS QD技術に基づいた単一電子ポンプをテストするために使用する手順について説明します。項3のものはISO6研究所で行われている間、サブセクション1及び2で説明したステップは、ISO5クリーンルームで行われます。周囲条件を連続的に制御されます。温度と湿度の公称値は、それぞれ、20±1℃、55%±5%に設定されています。

1.微細加工

- フィールド酸化物

- 以下に浸漬することによって、ウエハを清掃してください:ピラニアエッチング(10分)、脱イオン(DI)水(10分)、RCA-2溶液(DI水175ミリリットル、塩酸30ミリリットル、H 2 O 2 30ミリリットル、100℃で10分間)を水に10希釈し、脱イオン水(5分)、フッ化水素(HF)酸:1(10秒)、DI水(10分)。 HF( すなわち 、ゴーグル、PVCエプロン、とPVC手袋)を取り扱う際は防護服を使用してください。順に進みます。

- ウエハを配置900℃での酸化炉で、次のように段階的に酸化する:ドライO 2(10分)、湿潤O 2(40分)、ドライO 2(10分)、N 2(15分)。

- オーミックコンタクト

- フォトリソグラフィとエッチングの酸化を行います。

- 次のようにウエハ表面上に接着促進ヘキサメチルジシラザン(HMDS)の数nmの厚さの層を堆積させる:プリベークをホットプレート上で110℃で1分間、ガラスビーカーにHMDSの約50ミリリットル注ぎ、ビーカーを置きます真空チャンバ内のウエハは、避難、2分間待ちます。

- バックとウェハ(3,000〜5,000 rpmで、所望の厚さに応じて25〜40秒)の前面両側のフォトレジストの2-4μmの厚さの層をスピン。

- マスクアライナーで紫外光に露出させ(4-10秒を10mW / cm 2の厚さに抵抗するようによります)。 1分間110℃のホットプレート上でポストベーク。

- 次いで脱イオン水ですすぎ、1〜2分間の開発。 20分間O 2プラズマエッチングを行う(;入射パワー= 50 W;圧力= 340ミリトール反射電力を<1 W)。

- 緩衝HF酸エッチング溶液中で酸化物(15:1、4-5分、30℃で≈速度は20nm /分のエッチング)。脱イオン水(5分)ですすいでください。 N 2でブロー乾燥。

- アセトンに浸漬することにより、フォトレジストを除去します。イソプロパノール(IPA)で、その後、N 2でブロー乾燥すすいでください。

- (所望のドーピング濃度に応じて30〜45分間、N 2流量)リン源と1000℃の炉内でウェハを配置します。

- 脱イオン水(10分)ですすぎ、水で希釈したHF酸(1、3-4分間、30℃でのエッチング速度≈は40nm / minで10)で汚染された酸化物層を除去します。

- 1.1.2のように酸化します。

- フォトリソグラフィとエッチングの酸化を行います。

- ゲート酸化物

- 繰り返しは1.2.1と1.2.2を繰り返します。

- 800℃で、専用の炉内でウェハを置き、次のように段階的に酸化する:ドライO 2(10分)、Dichloroethylene + O 2(20分)、ドライO 2(所望の酸化物の厚さに応じて10〜30分)、N 2(15分)。

- オーミックコンタクトのメタライゼーション

- 手順を繰り返し1.2.1。

- 電子ビーム蒸発器内のウエハを配置します。 0.2〜0.5ナノメートル/秒、5×10 -6トルで100nmのアルミニウムを蒸発させます。

- 金属をリフトオフするために1時間80℃でホットプレート上でNメチル-2-ピロリドン(NMP)中にウェハを浸します。必要に応じて超音波攪拌を使用してください。 2分間IPAですすいでください。 N 2でブロー乾燥。

- 少なくとも15分間、400℃で形成ガスでアニール。

2.ナノ加工

- ウェーハダイシング

- いずれかが(ポリマーおよび紡糸パラメータの種類は、この段階では無関係である)保護コーティングとして機能するように、ウェハ上にレジストをスピン。

- 〜10×2 mm 2での個々のチップにウェハを切断するためにダイヤモンドチップダイサーを使用してください。

- クリーニング

- その後2分間IPAですすぎ、80℃のホットプレート上で1時間、NMP中に浸します。 N 2でブロー乾燥。

- 5分間O 2プラズマエッチングを行う(= 50 W入射電力、反射電力を<1 W)。

- アセトン、IPAでクリーンスピン(7,500 rpmで、30秒)

- アライメントマーカパターニング

- スピンポリメチルメタクリレート(PMMA 950k)はA4は(30秒が所望の厚さに応じて、5,000-7,500 rpm)をレジスト。典型的な加工厚≈150〜200ナノメートル。 90秒間180℃のホットプレート上にレジストを焼きます。

- 電子ビームリソグラフィを実施しています。次の書き込み条件を使用し= 30keVのビームエネルギー、ビーム電流≈30 PA、面積線量500〜650μC/ cm 2でのマーカーの大きさに応じて≈およびレジスト厚。

- (1:3)40〜60秒間、その後20秒間IPAですすぎ、メチルイソブチルケトン、IPA溶液のレジストの開発。 N 2銃でブロー乾燥。

- 場所電子ビーム蒸発器内のチップ。 0.2〜0.4ナノメートル/秒、5×10 -6トルでのTiの15 nmおよびPtを65ナノメートルを蒸発させます。

- ステップ1.4.3のように金属を持ち上げ。

- ステップのようにきれいなチップ2.2.2-2.2.3。

- ゲートパターニング

- スピンは、2.3.1のように抵抗します。

- 電子ビームリソグラフィを実施しています。 = 30 keVのビームエネルギー、ビーム電流≈30 PA、面積線量≈は500〜700μC/ cm 2の高解像度の特徴については、以下の書き込み条件を使用してください。低解像度の機能のための条件を書く:= 15 keVのビームエネルギー、ビーム電流≈10 nAの、面積線量400〜600μC/ cm 2の ≈。

- 2.3.3のようにレジストを開発します。

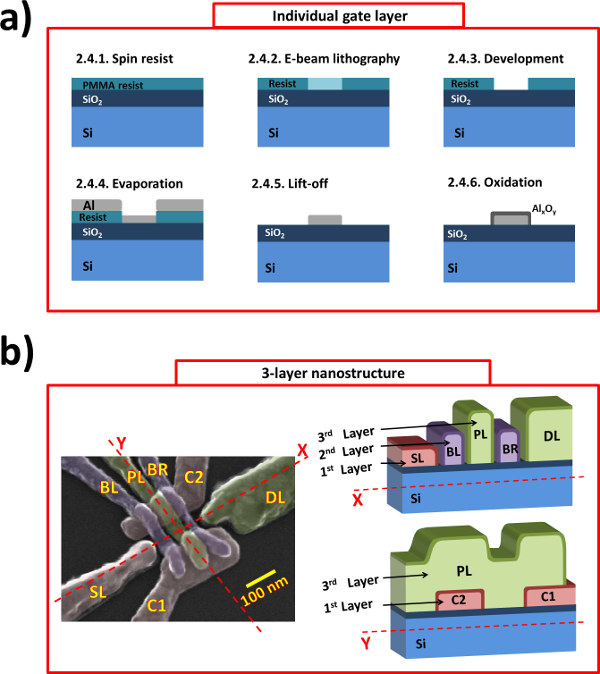

- 熱蒸発器内のチップを配置します。 0.1〜0.4ナノメートル/秒、1-9×10 -6ミリバールでのAlを蒸発させます。目標厚さは、レイヤ1のためのレイヤ数に応じて、 図2(b)に示すように(25〜35ナノメートル、レイヤ2、75〜90 45〜65 nmのために変化するn個レイヤ3のためのM)。

- ステップ1.4.3のように金属を持ち上げ。

- 5〜10分間、150℃のホットプレート上でのAlの酸化を行います。

- ステップ2.2.3のようにきれいなチップ。

- 手順を繰り返し二回3層ゲートスタックを実現する2.4.1-2.4.7。

3.デバイスのパッケージング

- ステップ2.1のようにサイコロチップ

- 2分間アセトン及びIPAの結果小さなチップをすすぎます。

- PMMA A5を有するプリント回路基板(PCB)の個片を接着。それが乾燥するために2分を待ちます。あるいは、熱化を強化するために、銀エポキシ樹脂を使用しています。

- ウェッジボンダにPCBをロードして、配線を進めます。

4.デバイスの完全性テスト

- ディッププローブに有線デバイスを含むPCBをマウントします。

- ディッププローブのものにPCBの電線を配線します。

- 液体ヘリウムを含む容器内にプローブを挿入します。過剰なヘリウムbを避けるために、ゆっくりと進みオイルオフ。

- 接地他のゲートを維持しながら、各デバイスのゲートについては、ソースメジャーユニットへのプローブの対応する室温の電極を接続してください。数NAにコンプライアンス電流を設定します。 、0.1 Vのステップで1.5Vにゼロからの電圧を掃引測定し、電流を記録します。

- バッテリ駆動の可変DC電圧源に各ゲート線を接続し、内蔵のロックインアンプの交流電圧源、及びロックイン増幅器の入力ポートにドレイン線にソース線。

- ( 図4参照)は、異なるゲート電圧の設定のためのコンダクタンスを排出するソースを測定します。

- グローバル接地C1とC2ゲートを維持することによりゲートBL、BR、PL、SLおよびDLに印加される電圧をランプアップ。 「ターン·オン」デバイス特性を記録します。

- 個別に各ゲート電圧を下降し、ゲート「ピンチオフ」の特性を記録します。

- 静電クを定義するためにゲート電圧を調整しますターンオン電圧より(大きい)、BLとBR(PL、SLおよびDL)の電圧を設定することによりアントゥムドット小さいです。クーロンブロッケード特性を記録します。

Representative Results

デバイス製造

初期の微細加工プロセス(プロトコルのサブセクション1)商業4インチ、高純度のシリコンウエハ上で実行される(n型不純物濃度≈10 12 cm -3で、抵抗率> 10kΩcm;厚さ= 310〜340ミクロン)。目的は、ゲート電極が堆積される基板を実現することです。この基板のフィールド酸化膜(ステップ1.1)、フィールド酸化膜(ステップ1.2)、高品質のゲート酸化膜(ステップ1.3)、及び金属化でキャップ真性領域でキャップのn +領域でキャップ真性領域からなるn +領域でありますオーミックコンタクト(ステップ1.4)。 図1A-Dは、微細加工プロセスの主要なステップを示す。 図1Eは、微細加工後の基板領域の顕微鏡画像を示します。この段階では、リソグラフィの最小フィーチャサイズは約4μmです。

のSiOステップ1.1において成長2酸化物層は、100nmの公称厚さを有し、保護層として使用されます。オーミック導体として作用するn型領域は、リン拡散によって得られます。 10〜20 cm -3で-ターゲットドーピング密度は約10 19です。選択ゲート誘電体として使用されるように成長させた高品質のSiO 2を 5nmの公称厚さを有します。ターゲット界面欠陥密度は<10 10 eVで-1 cm -2の中間ギャップです。専用の意図内蔵三重壁炉は、このプロセスのために使用されます。このシステムは、重金属イオン及び移動アルカリイオンによる汚染を最小限に抑えるだけでなく、酸化室へ拡散する水分を防止するように設計されています。電気接点を形成するために、アルミパッドは、n型領域の一部の上に電子ビーム蒸着によって堆積されます。

ナノファブリケーションプロセスは、(サブセクション2を参照)、チップ上で実行されるのsubstrステップ1で目的の処理されたウェハをダイシングすることにより得られるのATEは、静電MOS量子ドットを定義するために使用されるナノスケールのゲート電極を実現することです。各ナノファブリケーションの実行は、通常、10〜15完全なデバイスのサンプルを生成します。バッチあたり1~2デバイスの走査型電子顕微鏡写真(SEM)画像は、通常、EBLリソグラフィ段階が成功していることを確認するために行われます。 SEM画像は、基板や金属ゲートに電荷を注入し、漏れの原因となることがありますので、残りは電気的にテストされている間、デバイスのほんの数は、このようにチェックされています。この段階では、リソグラフィの最小フィーチャサイズは約35nmです。基板を回転ステージに取り付けられている間に堆積したAl膜の良好な均一性を達成するために、金属は、第二の数オングストローム/ほど遅い速度で蒸発させました。これは、室温で維持され、及びAlの結晶粒径は約20nmであると推定されている。 図2Aは nanofabricatioの主要なステップを示してn個のプロセス。 図2Bは、ゲート電極の正しい定義を確認しているSEM画像を示します。一般的に、人は直接可能な最小フィーチャサイズとQD(BL、BRおよびPL)を定義し、それらのゲートを実現することを目指しています。一方、電子リザーバ(DLとSL)を定義するために使用されるもののゲートはリードにおけるエネルギー準位の意図しない離散化を避けるために、より大きな寸法を有することができます。ステップ2.3において実現ナノスケールのTi / Ptのマーカーは、ゲートの3層の一貫したアラインメントのための参照として使用されます。プラチナは、電子ビーム中のSiO 2表面に対して優れたコントラストのために選択されます。チタンは、接着性を向上させるために使用されます。

製造プロセスの全ての段階において、炭素繊維の先端ピンセットは、破壊的な静電放電(ESD)の可能性を低減するために、チップを処理するために使用されます。

最後に、順番にINDIVIに電気的測定を実行しますデュアルデバイスは、各チップは、約2×2 平方ミリメートル(サブセクション3)の小片に切断する必要があります。それぞれの作品は、その後、そのピンAlワイヤを介してデバイスの電極に接続されているカスタムメイドのPCB(ロジャースR03010低損失誘電体)に接着されています。ワイヤボンディングは、チップを加熱することなくウェッジボンダ装置を用いて行われます。適切な結合パラメータの選択は、二つの検討事項に基づいています。一方、ワイヤボンディングは、熱のAl のy O x層を穿孔し、ゲートパッドとの良好な金属間接触を行う必要があります。一方、過度の機械的ストレスは、ゲートと原因基板漏れ下損害フィールド酸化パンチトラフイベントになることがあります。配線工程の間に、帯電防止ブレスレットの使用は、ESDを防止することをお勧めします。 図3では、6個々のデバイスとチップがPCB上に接着されます。

デバイスの完全性テスト

血友病そのような希釈冷凍機としてmKの温度測定装置をプラットフォームにロードeは、予備電気的試験は、試料の完全性を(プロトコルのサブセクション4を参照)を確認するために4.2 Kで行われます。この目的のために、PCBは、無酸素銅の筐体に挿入され、最終的に彼液体に浸漬される浸漬プローブに取り付けられています。

最初の試験は、典型的には、各ゲート上に順次実行されるリークテストです。他のものは、接地されている間、ソースメジャーユニットは、個々のゲート電極に接続されています。電圧は1.5 Vまで上昇され、電流ソースで測定されます。この電圧範囲内では、正常に動作してゲートをSiO 2層は、シリコン基板から金属を絶縁するとAl のy O xが重なるゲートを絶縁するために、行うことが想定されていません。典型的には、酸化膜破壊は、デバイスの幾何学的形状及び酸化物に応じて、4〜Vより大きい電圧に対して発生することが知られているTHICネス。現在、試験中に検出された場合にそのため、それは酸化物層の少なくとも1つが破損している可能性があり、デバイスを廃棄しなければなりません。通常、ゲートの10%未満の漏れを示します。収率は、ゲート電極の平面的な拡張の影響を受けることが知られています。特に、それは、ゲート - 基板漏れを持つことになる可能性が高いゲート酸化物領域とゲートの大きな重なり。同様に、大きく異なる層からゲート間のオーバーラップは、より可能性が高いゲート - ゲート漏れの発生があります。引用された収率は、薄い酸化物に、約0.5ミクロン2の層間のオーバーラップで約50μm2の面積を占めるゲートに関連します。

デバイスが初期漏れ試験に合格した後、ソースおよびドレインコンタクトは、増幅器におけるロックとモジュール制御電圧バッテリラックのゲートに接続されています。この構成では、デバイスは、oをオンします世界的に同時に全てのゲート電圧をランプアップされることによりn。電流をピンチオフする個々のゲートの能力を確認するために、高電圧で他の人を維持しながら次に、各ゲート電圧を個別にランプダウンされている。 図4(a)は、これらの測定の代表的なトレースを示しています。ソース - ドレイン伝導経路または個々のゲートピンチオフのいずれかが存在しないことは、多くの場合、ゲートの爆発や金属不連続としてゲート損傷のいくつかのタイプの指標です。

最後に、ソース-ドレイン電流は、クーロンブロッケード16( 図4B参照 )の署名を観察するソース-ドレインバイアスとプランジャゲート電圧の関数として測定されます。

測定結果

適切なデバイスが発見されると、それは、液体ヘリウム容器から除去し、ESDを引き起こし得る水分の形成を回避するために、ホットエアガンで乾燥させます。最後に、希釈冷凍機に転送されます。

<Pクラス= "jove_contentは">実験は約100 mKでのベース温度で自作プラスチック希釈冷凍機で行われます。クライオスタットは、4.2 Kヘリウム浴中に浸漬真空チャンバ内にあります。電気ラインも入ってくるヘリウム3の蒸気を凝縮するために使用される1 Kポットで熱化されています。混合室では、ヘリウム3-希薄相へのヘリウム3リッチ相からの3He原子の吸熱転送システムは、約100 mKでのベース温度に到達することを可能にします。図5に示すように、冷蔵庫20は、DC線および低温でデバイスに室温電子機器を接続するために使用される3高周波ラインが装備されています。 DCラインのファイブThermocoaxケーブルであり、15は、ツイストペア織機ワイヤです。これらの線はバッテリ駆動DC電圧源に試料のゲート電極を接続します。 RTでの電圧分割器は、個々のゲートに電気的ノイズを低減するために使用されます。 RFラインがある半剛性同軸ケーブルであります RTでブロックされた熱雑音とDCを低減するために4 Kで10 dB減衰。これらの行は、PCB上のバイアスティーのコプレーナ導波路に接続されています。

低雑音トランスインピーダンス増幅器及びデジタルマルチメータは、ポンプによって生成される電流を測定するために使用されます。電子機器は、接地ループの形成を防止するために、電池式オプトアイソレータを介してデバイスに接続されています。 RF駆動信号は、その接地直流成分ブロックを介してクライオスタットのいずれかから単離された任意波形発生器によって生成される( 図5参照)。

PCBは16純粋なDCラインと低温でDCおよびAC電圧を組み合わせるために使用する4バイアスティーの行が含まれています。 図3Bに示すように、RCディスクリート部品がT字接続(R =100kΩで、C = 10nFの)を実現するために使用され、50Ω整合集積コプレーナ導波路は、高周波信号の伝播のために使用されます。

e_content ">デバイスがmKの温度になると、ゲート電圧は、QDで単一電子占有率が達成されるように、特に、トンネル障壁は、ゲートBLとBRの下に形成されて調整され、電子の蓄積層がゲートの下に誘導されます蓄積ゲートはより大きいターン·オン電圧で分極されながらPL、SLとDL。このためには、バリアゲート電圧は、それらのターンオン値より低く設定されている。このようにQDゲートPLの下に形成されますその平面の延長はゲート、その電圧が、静電閉じ込めを誘導するために、それらのターンオン値以下に維持されるC1及びC2を介して制御される。次に、RF信号は、周期的に、トンネルバリア(複数可)の透明性、及び電気化学的に調節するためにオンにされますドットの潜在的なシングル電子ポンプは、1つまたは2つの正弦波駆動電圧を用いて達成される。一信号駆動の場合は、駆動信号が左側にトンネル障壁のポテンシャルを変調するゲートBLに印加されの - 側QD。二信号駆動の場合には、AC励起は、同じ周波数であるが異なる位相及び振幅を残しバリアとQDの両方の電位を調節するためにゲートBLとPLに印加されます。これらの追加の自由度が一つの電子移動13の方向を制御することを可能にします。反復プロセスは、典型的には、主曲実験パラメータ( すなわち 、RF駆動信号振幅/位相とDCゲート電圧)と最適な電流の量子化を達成するために必要とされます。 2つのポンプのプロトコルのいずれも電荷移動を実行するためのドレイン - ソースバイアスが必要であることに留意されたいです。従って、ソース電極及びドレイン電極は、ポンプ動作中に接地されている。 図6は、入力された障壁(BL)とプランジャ(PL)のゲートに、2つの信号の正弦波駆動を適用したEFの整数倍で特性の電流プラトーを示します。これらのデータは、T比較的低い駆動周波数(10 MHz)で採取されパラメータのuningは、高速に行うことができます。実際には、典型的には非常に微細なパラメータの最適化を必要とする13、数百MHzでポンプを作動させることが望ましいです。

図1.微細加工。(A)微細加工における主な工程の模式図。漫画は一定の縮尺で描かれていません。 (B)オーミックコンタクトのためのドープされた領域の実現。 (C)ゲート酸化物の実現。 (D)オーミックコンタクトのメタライゼーション。微細加工プロセスが完了した後、チップ上の個々のフィールドの(E)顕微鏡画像。フィールドのサイズは1.2×1.2ミリメートル2である。 この図の拡大版を表示するには、こちらをクリックしてください。

図2.ナノファブリケーション。個々のゲート層のための(A)製造プロセス。漫画は一定の縮尺で描かれていません。 (B)チャージポンプの実験に使用した3層のゲートナノ構造。左:測定に使用されるものと同様の装置のSEM像。右:XカットとYカットの両端の装置の模式的断面図。この図の拡大版を表示するには、こちらをクリックしてください。

サンプルの図3.電気的接続。プリント基板の(A)のレイアウト。バイアスティー(左)ANとPCB領域の(B)倍率Dの等価回路(右)。 (C)PCBへの電気的接続のために、チップホルダーとボンドワイヤ上に接着6個々のフィールドを持つチップ。 (D)ナノ加工後の個々のフィールドの顕微鏡画像。ゲート酸化物領域の中央にゲートのレイアウトの(E)SEM像。 この図の拡大版を表示するには、こちらをクリックしてください。

図4.予備試験。(A)ソース·ドレイン交流電流が異なるゲート電圧の関数としての(二乗平均平方根)。トレースは113.17 Hzで50μVRMSの励起によるロックインアンプを用いて測定されています。個々のゲート電圧の残りのゲート電圧は、V C1 = <以外は、2.0 Vに固定されているトレースプランジャゲート電圧とソース-ドレインバイアス電圧の関数としてのEMソース-ドレイン電流の> V C2 = 0.0 V.(B)のカラーマップのV SL = 1.5 V、V DL = 1.15 V、V BL = 0.78 V、 V BR = 0.85 V、V C1 = V C2 = 0.0 V. この図の拡大版を表示するには、こちらをクリックしてください。

図5.測定のセットアップの概略図。二十dcライン(緑)と3つの同軸RF線(黒)はPCBにRTエレクトロニクスを接続します。ソースコンタクト(赤色)が接地されているポンプ(紫)のドレインは、トランスインピーダンス増幅器および光アイソレータを介してデジタルマルチメータに接続されています。独立した接地接続(I異なる記号でndicated)電子計測器およびクライオスタット電気ラインに使用されている。 この図の拡大版を表示するには、こちらをクリックしてください。

図6.現在の量子化。ゲートBLとPLに適用されるF = 10 MHzで、2つの信号の正弦波駆動用にV PLの関数として現在の励起。位相差= 49度、V RF PL = V RF BL = 0.31 V PP。 EFの整数倍で、ポンピング台地の理想的な位置は赤い水平線として示されている。 この図の拡大版を表示するには、こちらをクリックしてください。

Discussion

本論文で報告されたプロトコルは、その機能の完全性をテストし、単電子ポンプとして、それらを動作させるために、シリコンMOSのQD、ならびに実験手順を製造するための技術について説明します。注目すべきことに、ゲート設計を調整することによって、同一の製造工程では、量子ビットの読み出しおよび制御17に適し、ならびに12,13チャージポンプデバイスを製造するために使用することができます。我々は、この記事で引用されたプロセスの多くのパラメータは(キャリブレーション、作るか、またはモデル)を使用し、製造ツールのと同様に、シリコン基板(厚さとバックグラウンドドーピング密度)の種類に応じて変えることができることに注意してください。そのようなリソグラフィ露光量または現像時間、エッチングや酸化時間等の数量は、慎重に較正されかつ信頼性の高い歩留まりを確保するためにテストされなければなりません。さらに、異なるプロセスのために同じ製造ツールの使用に起因するクロスコンタミネーションを避けるために重要です。この目的のために、数のCriticalステップはもっぱら、金属蒸発、酸素炉とHF浴などのシリコン処理専用の機器を用いて実施されます。

より一般的には、シリコンは、チャージポンプ18〜20を実現するための最適な材料として関心の高まりを描いています。これは、一部の業界互換のシリコンプロセスを使用して、新しい量子ベース電流の標準を実装する魅力的観点によるものです。これは、スケーラビリティ、並列駆動のオーバーヘッドのためのよく確立され、信頼性の高い統合技術の恩恵を受けるだろう。重要なことには、ゲート材料のような伝統的な金属を含まない完全な相補型MOS(CMOS)技術は、単一の電子デバイス21に大幅に減少した背景の電荷の変動を示しています。このような変動は計量精度を達成するために有害であることができます。

ここで説明するプロトコルは、金属ゲートを有するMOSナノデバイスの実現に制限されています。したがって、achieへ完全な産業適合性をまして電荷変動を低減するには、ゲート堆積技術を変更し、ゲート材料として高濃度にドープされた多結晶シリコンを使用するために必要とされるであろう。

結論として、ここで説明したMOS QDポンプは最近、正確な電流発生13の面で非常に優れた性能を有するシリコンの技術的利点を組み合わせています。これは、1つは、コンパクトで汎用性の高いシステムにつながる複数のゲート層を積層することを可能にする設計及び製造プロセスの高い柔軟性に由来します。一緒に背景の電荷の変動を減少させる可能性のあるドットの静電閉じ込めの結果として生じる微調整可能性は、他の半導体のポンプ22,23で観察された主な課題を克服するための段階を設定します。

Disclosures

著者らは、開示することは何もありません。

Acknowledgments

私たちは、有益な議論のためのKYタン、P.参照およびGC Tettamanziに感謝します。我々は、オーストラリアの研究評議会(認可番号DP120104710)、フィンランドアカデミー(認可番号251748、135794、272806)およびデバイス製造のためのオーストラリア国立加工施設からのサポートからの財政支援を認めます。 ARは、ニューサウスウェールズ大学の初期のキャリア研究の助成スキームからの財政支援を認めるものです。 MicroNova社ナノファブリケーションセンターのアールト大学の設備と技術サポートの提供も認められています。

Materials

| Name | Company | Catalog Number | Comments |

| Silicon wafers | TOPSIL | 4 inch | |

| Electron-beam lithography machine | Raith gmbh | Raith 150two | |

| E-beam resist | MicroChem gmbh | PMMA | |

| Photoresist | MicroChem gmbh | nLOF2020 | |

| Mask aligner | Quintel | Q6000 | |

| Photoresist developer | MicroChem gmbh | AZ826MIF |

References

- Sze, S. M. Physics of Semiconductor Devices. , Wiley. Interscience, NY. 505-566 (1969).

- Moore, G. E. Cramming More Components onto Integrated Circuits. Electronics. 38, 114-117 (1965).

- Voisin, B., et al. Few-Electron Edge-State Quantum Dots in a Silicon Nanowire Field-Effect Transistor. Nano Lett. 14 (4), 2094-2098 (2014).

- Asenov, A., Brown, A. R., Davies, J. H., Savas, K., Slavcheva, G. Simulation of Instrinsic Parameter Fluctuations in Decananometer and Nanometer-Scale MOSFETs. IEEE Trans Electron Devices. 50 (9), 1837-1852 (2003).

- Zwanenburg, F. A., et al. Silicon Quantum Electronics. Rev. Mod. Phys. 85 (3), 961-1019 (2013).

- Ladd, T. D., et al. Quantum computers. Nature. 464 (7285), 45-53 (2010).

- Piquemal, F. Genevès, G. for a direct realization of the quantum metrological triangle. Metrologia. 37 (3), 207-211 (2000).

- Angus, S. J., Ferguson, A. J., Dzurak, A. S., Clark, R. G. Gate-Defined Quantum Dots in Intrinsic Silicon. Nano Lett. 7 (7), 2051-2055 (2007).

- Gonzalez-Zalba, M. F., Heiss, D., Podd, G., Ferguson, A. J. Tunable aluminium-gated single electron transistor on a doped silicon-on-insulator etched nanowire. Appl. Phys. Lett. 101 (10), 103504-103501 (2014).

- Lim, W. H., et al. Observation of the single-electron regime in a highly tunable silicon quantum dot. Appl. Phys. Lett. 95 (24), 242102-242103 (2009).

- Yang, C. H., et al. Spin-valley lifetimes in silicon quantum dots with tunable valley splitting. Nat. Commun. 4 (2069), (2013).

- Chan, K. W., et al. Single-electron shuttle based on a silicon quantum dot. Appl. Phys. Lett. 98 (21), 212103-212101 (2011).

- Rossi, A., et al. An accurate single-electron pump based on a highly tunable silicon quantum dot. Nano Lett. 14 (6), 3405-3411 (2014).

- Pekola, J. P., et al. Single-electron current sources: Toward a refined definition of the ampere. Rev. Mod. Phys. 85 (4), 1421-1472 (2013).

- Giblin, S. P., et al. Towards a quantum representation of the ampere using single electron pumps. Nat. Commun. 3, 930 (2012).

- Kouwenhoven, L. P., Austing, D. G., Tarucha, S. Few-electron quantum dots. Rep. Prog. Phys. 64 (6), 701-736 (2001).

- Veldhorst, M., et al. An addressable quantum dot qubit with fault-tolerant control fidelity. Nat. Nanotech. 9 (12), 981-985 (2014).

- Fujiwara, A., Nishiguchi, K., Ono, Y. Nanoampere charge pump by single-electron ratchet using silicon nanowire metal-oxide-semiconductor field-effect transistor. Appl. Phys. Lett. 92 (4), 042102-1-042102-3 (2008).

- Jehl, X., et al. Hybrid Metal-Semiconductor Electron Pump for Quantum Metrology. Phys. Rev. X. 3 (2), 021012-1-021012-7 (2013).

- Tettamanzi, G. C., Wacquez, R., Rogge, S. Charge pumping through a single donor atom. New J. Phys. 16 (6), 063036-1-063036-17 (2014).

- Koppinen, P. J., Stewart, M. D., Zimmerman, N. M. Fabrication and Electrical Characterization of Fully CMOS-Compatible Si Single-Electron Devices. IEEE Trans Electron Devices. 60 (1), 78-83 (2013).

- Fletcher, J. D., et al. Stabilization of single-electron pumps by high magnetic fields. Phys. Rev. B. 86 (15), 155311-1-155311-6 (2012).

- Kataoka, M., et al. Tunable Nonadiabatic Excitation in a Single-Electron Quantum Dot. Phys. Rev. Lett. 106 (12), 126801-1-126801-4 (2011).