Protocol

주 :이 프로토콜은, 패키지 제작 실리콘 MOS QD 기술 기반 단 전자 펌프를 테스트하는 데 사용되는 절차를 설명한다. 섹션 3은 그 ISO6 실험실에서 수행되는 동안의 서브 섹션 1 및도 2에서 설명한 단계들은 ISO5 청정실에서 수행된다. 주변 조건은 지속적으로 제어된다. 온도와 습도에 대한 공칭 값은 각각 20 ± 1 ° C와 55 % ± 5 %로 설정되어있다.

1. 미세

- 필드 산화물

- 100 ° C에서 H에게, RCA-2 용액 (DI 물 175 ㎖, 염산 30 ㎖, 피라냐 에칭 (10 분간), 탈 이온수 (DI) 물 (10 분) 2 O 2 30 ㎖를 다음에 침지하여 웨이퍼를 청소 1 (10 초), DI 물 (10 분) : 10 분), 탈 이온수 (5 분), 물 (10)을 희석 불산 (HF) 산에 대한. HF (즉, 고글, PVC 앞치마, 및 PVC 장갑)을 취급 할 때는 보호 의류를 사용합니다. 정해진 순서대로 진행합니다.

- 웨이퍼를 배치다음 900 ℃에서 산화로에서 산화 단계 : 건식 O 2 (10 분), 습식 O 2 (40 분), 건조 O 2 (10 분), N 2 (15 분).

- 옴 연락처

- 포토 리소그래피 및 에칭 산화물을 수행하십시오.

- 다음, 웨이퍼 표면 위에 접착 촉진 헥사 메틸 디 실라 잔 (HMDS)의 몇 나노 미터의 두께로 층을 증착 : 프리 베이크를 핫 플레이트상에서 110 ℃에서 1 분 동안, 유리 비이커에 HMDS의 ~ 50 ㎖에 붓고, 비커를 놓고 그리고 진공 챔버 내에서 웨이퍼가 대피 2 분 동안 기다린다.

- (25 ~ 40 초 원하는 두께에 따라 3,000-5,000 RPM) 뒷면과 앞면 웨이퍼의 양쪽에 포토 레지스트의 2-4 μm의 두꺼운 층을 스핀.

- (레지스트 두께에있어서, 4-10 초 동안 10 mW의 / cm 2)의 마스크 얼 라이너에서 자외선에 노출시킨다. 1 분 동안 110 ° C에서 열판에 포스트 - 빵.

- 다음 탈 물에 씻어, 1 ~ 2 분 동안 개발한다. 20 분 동안 O 2 플라즈마 에칭을 수행한다 (; 입사 전력 = 50 W; 압력 = 340 mTorr의 반사 전력을 <1 W).

- 버퍼링 된 HF 산 에칭 용액에서 산화물 (15 : 1 ~ 5 분, 30 ° C에서 20 ≈ 율 ㎚ / 분을 에칭). 탈 이온수 (5 분)에서 씻어. N 2와 건조 불어.

- 아세톤에 침지하여 포토 레지스트를 제거합니다. 이소프로판올 (IPA)에, 다음 N 2로 바람을 불어 건조 씻어.

- (원하는 도핑 밀도에 따라 30 ~ 45 분 동안 N 2 흐름) 인 소스와 1,000 ℃에서 가열로에 웨이퍼를 놓습니다.

- 탈 이온수 (10 분)에 린스 : 물에 희석 HF 산 (1, 3 ~ 4 분, 30 ℃에서 에칭 속도 ≈ 40 나노 / 10 분)로 오염 된 산화물 층을 제거합니다.

- 1.1.2에서와 같이 산화.

- 포토 리소그래피 및 에칭 산화물을 수행하십시오.

- 게이트 산화물

- 반복 1.2.1와 1.2.2 단계를 반복합니다.

- 다음과 같이 800 ° C에서 전용로에서 웨이퍼를 놓고 단계에서 산화 : 건조 O 2 (10 분), D를ichloroethylene + O 2 (20 분), 건조 O 2 (10 ~ 30 분 원하는 산화막 두께에 따라 다름), N 2 (15 분).

- 옴 연락처 금속 화

- 단계를 반복 1.2.1.

- 전자 빔 증발기에 웨이퍼를 놓습니다. 0.2 ~ 0.5 nm의 / 초 5 × 10 -6 토르에서 알루미늄을 100 nm의 증발.

- 금속을 떠, 1 시간 동안 80 ℃에서 핫 플레이트상에서의 N 메틸 -2- 피 롤리 돈 (NMP)에 웨이퍼를 담근다. 필요한 경우 초음파 교반을 사용합니다. 2 분 동안 IPA에 씻어. N 2와 건조 불어.

- 적어도 15 분 동안 400 ℃에서 가스를 형성 어닐링.

2. 나노

- 웨이퍼 다이 싱

- 임의의 보호 코팅의 역할을하도록 웨이퍼 상에 레지스트 (중합체 및 회전 파라미터의 타입이 단계에서 부적합하다) 스핀.

- ~ 10 × 2mm 2의 개별 칩으로 웨이퍼를 절단하는 다이아몬드 팁의 다이 서 사용합니다.

- 청소

- 80 ° C에서 열판에 1 시간 동안 NMP에 흠뻑 젖어, 다음 2 분 동안 IPA에 헹군다. N 2와 건조 불어.

- 5 분 동안 O 2 플라즈마 에칭을 수행하여 (= 50 W 입사 전력, 반사 전력을 <1 W).

- 아세톤과 IPA로 깨끗한 스핀 (7,500 rpm으로, 30 초)

- 정렬 마커의 패터닝

- 스핀 폴리 메틸 메타 크릴 레이트 (PMMA 950K)는 A4는 (30 초는 원하는 두께에 따라 5,000-7,500 RPM)로 레지스트. 일반적인 작업 두께 ≈ 150 ~ 200 nm의. 베이킹 90 초 동안 180 ℃에서 핫 플레이트상에서 레지스트.

- 전자 빔 리소그래피을 수행. 다음의 기록 조건 사용 = 30 keV의 에너지 빔, 빔 전류 ≈ 30 펜실베이니아 영역 도즈 500-650 μC / cm 2 마커 크기에 따라 두께를 ≈ 레지스트.

- (3 1) 40 ~ 60 초, 20 초 후, IPA로 린스 메틸 이소 부틸 케톤과 IPA 용액에 레지스트 개발. N 2 총을 가진 건조 불어.

- 장소전자빔 증발기 칩. 티의 15 nm의 0.2 ~ 0.4 nm의 / 초에서 백금의 65 나노 및 5 × 10-6 Torr의 증발.

- 단계 1.4.3에서와 같이 금속을 들어 올립니다.

- 단계 2.2.2-2.2.3에서와 같이 청소 칩.

- 게이트 패턴

- 스핀은 2.3.1에서와 같이 저항.

- 전자 빔 리소그래피을 수행. = 30 keV의 빔 에너지, 빔 전류 ≈ 30 PA의 영역 용량 ≈가 500-700 μC / ㎠ : 고해상도 기능에 대한 다음과 같은 기록 조건을 사용합니다. 낮은 해상도 기능에 대한 조건을 쓰기 = 15 keV의 빔 에너지, 빔 전류 ≈ 10 nA의, 지역 용량 400 ~ 600 μC / ㎠ ≈.

- 2.3.3에서와 같이 저항 개발한다.

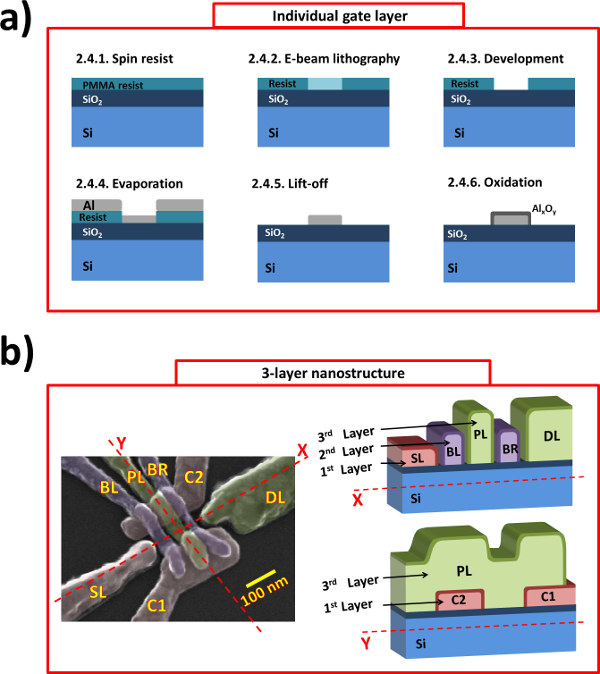

- 열 증발기에 칩을 놓습니다. 0.1-0.4 나노 미터 / 초 1-9 × 10 -6 mbar에서 알을 증발. 도 2B (레이어 1 내지 25-35, 계층 2 내지 45-65에 나타낸 바와 같이, 목표 두께는 층의 수에 따라 변한다 75-90 N레이어 3에 대한 M).

- 단계 1.4.3에서와 같이 금속을 들어 올립니다.

- 5-10 분 동안 150 ℃에서 핫 플레이트상에서 Al의 산화를 수행한다.

- 단계 2.2.3에서와 같이 청소 칩.

- 반복 단계는 배 3 층 게이트 스택을 실현할 2.4.1-2.4.7.

3. 장치 포장

- 단계 2.1에서와 같이 주사위 칩

- 2 분 동안 아세톤과 IPA의 결과 작은 칩을 씻어.

- PMMA A5와 인쇄 회로 기판 (PCB)에 개별적 단편 접착제. 이 마를 때까지 2 분을 기다립니다. 또한, thermalization을 향상시키기 위해, 실버 에폭시를 사용합니다.

- 웨지 본더에 PCB를로드하고 배선 진행합니다.

4. 장치 무결성 테스트

- 딥 프로브에 유선 장치를 포함하는 인쇄 회로 기판을 탑재합니다.

- 딥 프로브들로 PCB의 전기적 배선 라인.

- 액체 헬륨이 들어있는 용기에 프로브를 삽입합니다. 과도한 헬륨 B를 피하기 위해 천천히 진행오일 오프.

- 접지 된 다른 게이트들을 유지하면서 각 장치의 게이트를 들어, 소스 측정 유닛에 대응하는 탐침의 상온 전극을 연결한다. 몇 nA의에 준수 전류를 설정합니다. 0.1 V의 단계로 0에서 1.5V의 전압을 스윕 측정 전류를 기록한다.

- 배터리로 구동되는 가변 직류 전압원에 각 게이트 선을 연결하는 소스 선 내장 종속 증폭기의 교류 전압원과 종속 증폭기의 입력 포트에 드레인 선.

- 다른 게이트 전압 구성 (도 4 참조)에 대한 컨덕턴스를 드레인 소스를 측정한다.

- 세계적으로 접지 된 C1 및 C2 게이트를 유지함으로써 게이트 (BL), BR, PL, SL 및 DL에 적용되는 전압을 램프 업 (ramp up). '턴 - 온'장치 특성을 기록합니다.

- 개별적으로 게이트 전압을 램프 다운 및 게이트 '핀치 오프'특성을 기록한다.

- 정전 한때를 정의하는 게이트 전압을 조정턴온 전압보다 BL 및 BR (PL, SL 및 DL) 작은 (큰)에 전압을 설정하여 antum 점. 쿨롱 봉쇄 특성을 기록합니다.

Representative Results

디바이스 제조

초기 미세 가공 (프로토콜의 하위 섹션 1) 상용 4 인치 고순도 실리콘 웨이퍼 상에 수행된다 (n 형 도핑 농도 ≈ 10 12cm -3, 비저항> 10 kΩcm; 두께 = 310~340 ㎛의 ). 목표는 게이트 전극이 증착 될 기판에를 실현하는 것이다. 이 기판은 필드 산화물 (단계 1.1), 필드 산화물 (단계 1.2), 고품질의 게이트 산화물 (130 단계) 캡핑 진성 영역으로 캡핑 N + 영역으로 캡핑 진성 영역 이루어지는되고, 금속 N + 영역에 대한 옴 접촉 (단계 140).도 1a-D는 마이크로 프로세스의 주요 단계들을 도시한다.도 1E는 기판의 미세 가공 후의 필드의 현미경 이미지를 도시한다. 이 단계에서 리소그래피의 최소 피처 크기가 약 4 ㎛ 인 것이다.

그런가단계 1.1에서 성장이 산화물 층은 100nm의 공칭 두께를 가지며, 보호 층으로서 사용된다. 오믹 도전 체로서 작용 n 형 영역 인 확산을 통해 얻어진다. 10 20cm -3 - 타겟 도핑 농도는 약 1019이다. 선택적으로, 게이트 유전체로 사용될 성장 고품질의 SiO2를 5 nm의 공칭 두께를 갖는다. 목표 계면 결함 밀도는 <10 10 cm -2 -1 eV의 중간 갭이다. 헌신적이고 의도적으로 내장 트리플 벽로이 과정에 사용됩니다. 이러한 시스템은 중금속 이온 및 이동 알칼리 이온으로 오염을 최소화뿐만 아니라, 산화 챔버 내로 확산되는 습기를 방지하도록 설계된다. 전기 접점을 형성하기 위해, 알루미늄 패드는 n- 형 영역의 일부에 전자빔 증착을 통해 증착된다.

나노 제조 공정은 (하위 섹션 2 참조) 칩상에서 수행된다 SUBSTR단계 1. 목표 처리 웨이퍼를 다이 싱하여 얻어진 축열 정전 기적 MOS 양자점을 정의하는 데 나노 크기의 게이트 전극을 실현하는 것이다. 각각의 나노 실행은 일반적으로 10 ~ 15 완료 디바이스 샘플을 생산하고 있습니다. 주사 전자 현미경 배치 당 1-2의 장치 (SEM) 이미지는 일반적 EBL 리소그래피 단계가 성공적으로되었는지 확인하기 위해 수행된다. SEM 영상은 기판 또는 금속 게이트에 전하를 주입하고 누설이 발생할 수 있기 때문에, 나머지는 전기적 테스트 동안, 장치의 단지 소수,이 방법으로 판정한다. 이 단계에서 리소그래피의 최소 피처 크기가 약 35 ㎚이다. 기판 회전 스테이지 상에 장착되는 동안 증착 된 알루미늄 필름의 양호한 균일 성을 달성하기 위해, 금속은, 제 몇 옹스트롬 /만큼 느린 속도로 증발시킨다. 이것은 RT로 유지되고, Al의 입경은 약 20 nm 인 것으로 추정된다.도 2a는 nanofabricatio의 주요 단계들을 도시N 프로세스.도 2b는 게이트 전극의 정확한 정의가 확인되는 SEM 이미지를 보여준다. 일반적으로, 사람은 가능한 최소 피처 크기와 직접 QD 정의 그 게이트 (BL, BR 및 PL)을 실현하는 것을 목적으로한다. 대조적으로, 전자 저장소 (DL 및 SL)을 정의하는 데 사용되는 게이트 리드들에서의 에너지 레벨들의 의도 이산화을 피하기 큰 치수를 가질 수있다. 단계 2.3에서 실현 나노 크기의 Ti / Pt를 마커 게이트의 3 개의 층으로 일관 정렬을위한 참고 자료로 사용된다. 백금은 전자 빔에서의 SiO2 표면에 대해 우수한 콘트라스트를 위해 선택된다. 티타늄은 접착 성을 향상시키기 위해 사용된다.

제조 공정의 모든 단계에서, 탄소 섬유 팁 핀셋 파괴 정전기 방전 (ESD)의 가능성을 줄이기 위하여, 칩을 처리하기 위해 사용된다.

마지막 순서 INDIVI에 전기적 측정을 수행이중 디바이스는, 각각의 칩은 약 2 × 2 ㎜ × 2 (하위 섹션 3)의 더 작은 조각으로 절단 할 필요가있다. 각 조각은 그 핀들 Al의 전선을 통해 소자 전극에 접속된다 주문품 PCB (로저스 R03010 저손실 유전체)에 접착된다. 와이어 본딩은 칩을 가열하지 않고 웨지 본더 기계로 수행된다. 적합한 본딩 파라미터의 선택은 두 고려 사항에 기초한다. 한편, 와이어 본드는 열 알의 Y O X의 층을 관통하고 상기 게이트 패드와 양호한 금속 - 금속 접촉을 할 필요가있다. 한편, 과도한 기계적 응력이 손상되는 원인이 게이트와 기판 누설 하부 필드 산화물을 펀치 쓰루 이벤트를 초래할 수있다. 배선 공정 중에 대전 팔찌의 사용은 ESD를 방지하는 것이 바람직하다. 그림 3에서 6 개별 장치와 칩은 인쇄 회로 기판에 접착된다.

장치 무결성 테스트

befor를이러한 희석 냉동기 mK의 온도 측정 플랫폼에 장치를 로딩 E는 예비 전기 시험은 시료의 무결성 (프로토콜의 하위 섹션 4 참조)을 확인하기 위하여 4.2 K에서 수행된다. 이를 위해, PCB는 무산소 구리 인클로저에 삽입되어 결국 그 액체에 침지 딥 프로브 상에 장착된다.

초기 검사는 일반적으로 각 게이트에 순차적으로 수행되는 누설 테스트입니다. 다른 접지되는 동안 소스 측정 유닛은 각각의 게이트 전극에 접속된다. 전압을 1.5 V까지 증가하고 전류 소스에서 측정된다. 이 전압 범위 내에서 적절하게 작동 게이트의 SiO2 층은 실리콘 기판으로부터 금속으로 절연와 Al y는 O X가 중첩 게이트를 절연한다 때문에, 실시 안된다. 일반적으로 산화 분해는 장치의 형상과 산화 thic에 따라 전압을 위해 ~ 4 V보다 크게 발생하는 것으로 알려져 있습니다kness. 전류 시험 중에 검출되는 경우, 따라서, 이는 산화물 층의 적어도 하나가 손상되는 가능성이 장치가 폐기되어야한다. 통상적으로, 게이트의 10 % 미만은 누출을 나타낸다. 수율은 게이트 전극의 평면 확장에 의해 영향을받는 것으로 알려져있다. 특히,이 게이트 - 기판 누출을 가지고있을 것 일수록 게이트 산화물 영역과 게이트 큰 오버랩. 마찬가지로, 상이한 계층에서 게이트 게이트 - 게이트 누설의 가능성이 발생 사이의 더 큰 중첩이있을 것이다. 인용 수율은 얇은 산화물에 약 50 μm의 (2)의 영역을 차지 게이트 관련이 층간에 약 0.5 μm의 2의 겹칩니다.

장치가 초기의 누설 테스트를 통과하면, 소스 및 드레인 콘택트는 증폭기의 잠금 및 모듈러 제어 전압 배터리 선반 게이트에 접속된다. 이 구성에서, 장치 O를 온전 세계적으로 동시에 모든 게이트 전압을 올렸하여 N. 전류를 핀치 오프 개별 게이트의 능력을 확인하기 위해 높은 전압에서 다른 유지하면서 다음에, 각각의 게이트 전압이 개별적으로 램핑 다운된다.도 4a는 이러한 측정치를 나타내는 흔적을 나타낸다. 소스 - 드레인 도통 경로 또는 개별 게이트 핀치 오프 중 하나의 부재는 종종 게이트 폭발 또는 금속 불연속성 게이트 손상의 어떤 타입의 표시이다.

마지막으로, 소스 - 드레인 전류는 쿨롱 봉쇄 (16) (도 4b 참조)의 특성을 관찰하는 소스 - 드레인 바이어스 및 플런저 게이트 전압의 함수로서 측정된다.

측정

적절한 장치가 발견되면, 그것은 그 액체 용기로부터 제거하고, ESD의 원인이 수분의 형성을 방지하기 위해 열풍 건으로 건조시킨다. 마지막으로,이 희석 냉동기로 전달된다.

<P 클래스 = "jove_content은"> 실험은 약 100 mK의베이스의 온도 자체 제작 플라스틱 희석 냉동기에서 수행된다. 저온 유지 장치는 4.2 K 헬륨 조에 침지 진공 챔버이다. 전기 라인도 들어오는 3He 증기를 응축하기 위해 사용되는 1 K 냄비에 thermalized된다. 혼합 챔버에서 3He - 희석 단계로 3He 풍부 상으로부터 3He 원자의 흡열 전달이 시스템은 약 100 mK 인베이스의 온도에 도달 할 수있다.도 5에 도시 된 바와 같이, 냉장고 (20)는 DC 선 및 저온 장치 상온 전자를 연결하는 데 사용되는 3 RF 라인을 갖추고있다. DC 라인 중 5 Thermocoax 케이블이고 15 쌍 직기 와이어를 꼬아. 이 선은 배터리 전원 DC 전압 소스에 시료의 게이트 전극을 연결한다. RT에서의 전압 분배기 개별 게이트에 전기적 잡음을 감소시키기 위해 사용된다. RF 선은 동축 케이블이다 반 강체 RT에서 차단 및 열 잡음을 감소시키는 DC 4 K에서 10 dB만큼 감쇄. 이 라인은 PCB에 바이어스 티의 코 플레너 도파로에 접속된다.

저잡음 트랜스 임피던스 증폭기 및 디지털 멀티 미터는 펌프에 의해 발생 된 전류를 측정하기 위해 사용된다. 전자는 접지 루프의 형성을 방지하기 위해 배터리 전원 공급 장치를 통해 광 분리기에 연결된다. RF 구동 신호가 그의 접지 DC 블록 성분을 통해 저온 유지 장치 중 하나에서 분리되는 임의 파형 발생기에 의해 생성된다 (도 5 참조).

인쇄 회로 기판 (16) 순수한 직류 라인과 낮은 온도에서 DC 및 AC 전압을 결합하는 데 사용되는 4 바이어스 티 라인이 포함되어 있습니다. 도 3b에 도시 된 바와 같이, RC 개별 컴포넌트는 티 연결 (R = 100 kΩ에서, C = 10 nF이다)를 실현하기 위해 사용되며, (50), 고주파 신호의 전파에 이용되는 통합 된 공면 도파관 Ω는 정합.

e_content "> 장치 mK의 온도가되면, 게이트 전압이 QD에 단 전자 점유도가 달성되도록. 특히, 터널 장벽 게이트 BL과 BR 아래에 형성되어 조정되고, 전자 축적 층이 게이트 아래 유도 축적 게이트들이 편파하면서 PL, SL 및 DL은.이를 위해, 배리어 게이트 전압이 자신의 턴온 값 미만으로 설정되어보다 큼 - 턴 - 온 전압. QD 게이트 PL 아래에 형성되는 이러한 방식으로 그 평면 확장은 다음에, RF 신호는 주기적 터널 장벽 (들)의 투명도를 조절하기 위해 턴온된다. 그 전압 정전기 가둠을 유도하는 그들의 턴온 값 이하로 유지되는 게이트들 C1 및 C2를 통해 제어하고, 전기 화학적 도트의 전위. 단 전자 펌핑은 하나 또는 두 개의 정현파 구동 전압을 얻을 수있다. 하나의 신호 구동의 경우에는, 구동 신호는 왼쪽에서 터널 장벽의 전위를 변조 게이트 BL에인가 의 - 측QD. 두 신호 구동의 경우에, 교류 기진은 동일한 주파수이지만 서로 다른 위상과 진폭으로 왼쪽 장벽 QD 양의 전위를 조절하는 게이트 및 PL BL에인가된다. 이러한 추가의 자유도는 하나의 전자 이동 (13)의 방향을 제어 할 수있다. 반복 프로세스는 통상적으로 튜닝 메인 실험 파라미터 (즉, RF 구동 신호 진폭 / 위상 및 DC 게이트 전압) 및 전류 최적 양자화를 달성하는데 필요하다. 두 펌핑 프로토콜 중 어느 것도 전하 전송을 수행하는 드레인 - 소스 바이어스가 필요합니다. 따라서, 소스 및 드레인 전극은 펌프 동작 동안 접지된다.도 6을 나타낸다 입력 배리어 (BL)과 플런저 (PL)의 게이트에 두 신호 정현파 구동을 적용함으로써 얻어지는 EF의 정수배의 특성 전류 고원이. 이러한 데이터는 T의 상대적으로 낮은 구동 주파수 (10 메가 헤르츠)에서 촬영 내부 튜닝 파라미터 빨리 수행 될 수있다. 실제로, 이것은 통상적으로 훨씬 더 미세한 최적화 파라미터 (13)를 요구하는, 수백 MHz에서 펌프를 작동시키는 것이 바람직하다.

미세 주요 단계의 그림 1. 마이크로. (A) 도식 그림. 만화는 비율로 도시되지 않습니다. 옴 접촉을위한 도핑 영역 (B)를 실현. (C) 게이트 산화물의 실현. 옴 접촉의 (D) 금속 화. 미세 가공 후에 칩의 개별 필드 (E) 현미경 이미지가 완성된다. 이 필드의 크기는 1.2 X 1.2 mm의 2입니다. 이 그림의 더 큰 버전을 보려면 여기를 클릭하십시오.

개별 게이트 층 그림 2. 나노. (A) 제조 공정. 만화는 비율로 도시되지 않습니다. (B) 전하 펌핑 실험에 사용되는 3 층 게이트 나노 구조물. 왼쪽 : 측정에 사용 된 것과 유사한 디바이스의 SEM 이미지. 오른쪽 :. X 컷 및 Y 컷에서 장치의 회로도는 단면도 이 그림의 더 큰 버전을 보려면 여기를 클릭하십시오.

도 3의 샘플에 전기 연결. 인쇄 회로 기판 (A) 레이아웃. (B) (왼쪽) 바이어스 - 티와 PCB의 영역의 확대D 등가 회로 (오른쪽). PCB에 전기 연결을위한 칩 홀더 및 본드 와이어에 붙어 6 개별 필드 (C) 칩. (D) 나노 후 개별 필드의 현미경 이미지. 게이트 산화물 영역의 중앙에 게이트 레이아웃 (E) SEM 이미지. 이 그림의 더 큰 버전을 보려면 여기를 클릭하십시오.

도 4 예비 시험. (A) 소스 - 드레인 AC 전류는 상이한 게이트 전압의 함수로서 (실효 값). 추적은 113.17 Hz에서 50 μV RMS를 여기에 종속 앰프 측정된다. 개별 게이트 전압의 남은 게이트 전압 V (C1) = <을 제외하고, 2.0 V로 고정되어 추적EM> V C2 = 플런저 게이트 전압과 소스 - 드레인 바이어스 전압. V의 SL의 기능 = 1.5 V, V DL = 1.15 V, V BL = 0.78 V로서 소스 - 드레인 전류의 0.0 V. (B) 컬러 맵, V BR = 0.85 V는 V (C1) = V (C2) = 0.0 (V) 이 그림의 더 큰 버전을 보려면 여기를 클릭하십시오.

측정 그림 5. 도식 설정. 스물 직류 라인 (녹색)과 세 개의 동축 RF 라인 (블랙) PCB에 RT 전자를 연결합니다. 소스 접촉 (적색)이 접지되는 동안 펌프 (보라색)의 드레인은 트랜스 임피던스 증폭기 및 광 아이솔레이터를 통해 디지털 멀티 미터에 접속된다. 별도의 접지 연결 (I다른 기호로 ndicated) 전자 계측 및 저온 유지 장치 전기 라인에 사용된다. 이 그림의 더 큰 버전을 보려면 여기를 클릭하십시오.

그림 6. 현재 양자화. 게이트 (BL) 및 PL에 적용 F = 10 MHz에서 두 신호 사인파 드라이브 V (PL)의 함수로 현재 양수. 위상차 = 49 °, V RF (PL) = V RF (BL) = 0.31 V 쪽. EF의 정수 배수에서 펌핑 고원의 이상적인 위치는 빨간색 가로 선으로 표시됩니다. 이 그림의 더 큰 버전을 보려면 여기를 클릭하십시오.

Discussion

이 논문에보고 된 프로토콜은 무결성 기능을 시험하는 단 전자 펌프로 작동하는 실리콘 MOS 양자점뿐만 아니라 실험 절차를 제조하는 기술을 설명한다. 놀랍게도, 게이트 설계를 조정하여, 동일한 제조 공정 12,13 펌핑 양자 비트 및 판독 제어부 (17)에 적합한 장치뿐만 아니라, 전하를 생성하기 위해 사용될 수있다. 우리는이 문서에서 인용 된 공정 변수의 많은 사람들이 사용하는 제작 도구에 따라 다를 수 있습니다 (교정, 또는 모델)뿐만 아니라, 실리콘 기판 (두께 및 배경 도핑 밀도)의 종류에. 이러한 리소그래피 노광량이나 현상 시간, 에칭, 산화 등의 시간 양들은 신중 보정 수율과 신뢰성을 보장하기 위해 테스트되어야한다. 또한, 다른 공정에서 동일 제조 도구의 사용으로 인한 오염을 방지하는 것이 중요하다. CR의이를 위해, 다수itical 단계는 금속 증발기, 산소 용광로 및 HF 화장실로 독점적으로 실리콘 처리 전용 장비로 수행된다.

보다 일반적으로, 실리콘은 전하 펌프 18-20을 실현하기 원하는 물질로서 관심이 증가 드로잉된다. 이는 산업 호환 실리콘 프로세스를 이용하여 새로운 양자 기반 전류 표준을 구현하는 매력적인 관점에 부분적으로있다. 이것은 확장 성, 병렬 운전 오버 헤드 잘 구축하고 신뢰할 수있는 통합 기술 혜택을 누릴 것입니다. 중요한 것은, 게이트 재료와 같은 전통적인 금속 프리 완전 상보 MOS (CMOS) 기술은, 단 전자 소자 (21)에 크게 감소 백그라운드 전하의 변동을 도시하고있다. 이러한 변동은 계량 정확도를 달성 해가 될 수 있습니다.

여기서 설명하는 프로토콜은 금속 게이트와 MOS 나노 디바이스의 실현에 한정된다. 따라서, achie하기전체 산업 호환 적이 전하의 변동을 감소, 그것은 게이트 증착 기술을 수정하고 상기 게이트 재료로 고농도로 도핑 된 다결정 실리콘을 사용하는 것이 필요하다.

결론적으로, 여기에서 논의 된 MOS QD 펌프는 최근에 정확하고, 현재 세대 (13)의 측면에서 아주 좋은 성능을 실리콘의 기술적 장점을 결합했다. 이것은 하나의 콤팩트하고 다양한 방식으로 이어지는 복수의 게이트 층을 적층 할 수 있도록 설계 및 제조 공정의 유연성에 기인. 백그라운드 전하의 변동을 줄일 수있는 가능성과 함께 도트 정전 감금 얻어진 미세 조정 기능은 다른 반도체 관찰 주요 도전 22,23 펌프 극복 스테이지를 설정한다.

Disclosures

저자가 공개하는 게 없다.

Acknowledgments

우리는 유용한 토론 켄터키 탄, 경찰 참조 및 GC Tettamanzi 감사합니다. 우리는 장치 제조를위한 호주 국립 제조 설비의 재정 호주 연구 협의회 (부여 번호 DP120104710), 핀란드의 아카데미 (부여 번호 251748, 135794, 272806)의 지원과 지원을 인정합니다. AR은 뉴 사우스 웨일스 대학의 초기 경력 연구원 그랜트 방식에서 재정 지원을 인정합니다. 하여 Micronova 나노 센터 알토 대학의 시설 및 기술 지원의 제공도 인정 받고 있습니다.

Materials

| Name | Company | Catalog Number | Comments |

| Silicon wafers | TOPSIL | 4 inch | |

| Electron-beam lithography machine | Raith gmbh | Raith 150two | |

| E-beam resist | MicroChem gmbh | PMMA | |

| Photoresist | MicroChem gmbh | nLOF2020 | |

| Mask aligner | Quintel | Q6000 | |

| Photoresist developer | MicroChem gmbh | AZ826MIF |

References

- Sze, S. M. Physics of Semiconductor Devices. , Wiley. Interscience, NY. 505-566 (1969).

- Moore, G. E. Cramming More Components onto Integrated Circuits. Electronics. 38, 114-117 (1965).

- Voisin, B., et al. Few-Electron Edge-State Quantum Dots in a Silicon Nanowire Field-Effect Transistor. Nano Lett. 14 (4), 2094-2098 (2014).

- Asenov, A., Brown, A. R., Davies, J. H., Savas, K., Slavcheva, G. Simulation of Instrinsic Parameter Fluctuations in Decananometer and Nanometer-Scale MOSFETs. IEEE Trans Electron Devices. 50 (9), 1837-1852 (2003).

- Zwanenburg, F. A., et al. Silicon Quantum Electronics. Rev. Mod. Phys. 85 (3), 961-1019 (2013).

- Ladd, T. D., et al. Quantum computers. Nature. 464 (7285), 45-53 (2010).

- Piquemal, F. Genevès, G. for a direct realization of the quantum metrological triangle. Metrologia. 37 (3), 207-211 (2000).

- Angus, S. J., Ferguson, A. J., Dzurak, A. S., Clark, R. G. Gate-Defined Quantum Dots in Intrinsic Silicon. Nano Lett. 7 (7), 2051-2055 (2007).

- Gonzalez-Zalba, M. F., Heiss, D., Podd, G., Ferguson, A. J. Tunable aluminium-gated single electron transistor on a doped silicon-on-insulator etched nanowire. Appl. Phys. Lett. 101 (10), 103504-103501 (2014).

- Lim, W. H., et al. Observation of the single-electron regime in a highly tunable silicon quantum dot. Appl. Phys. Lett. 95 (24), 242102-242103 (2009).

- Yang, C. H., et al. Spin-valley lifetimes in silicon quantum dots with tunable valley splitting. Nat. Commun. 4 (2069), (2013).

- Chan, K. W., et al. Single-electron shuttle based on a silicon quantum dot. Appl. Phys. Lett. 98 (21), 212103-212101 (2011).

- Rossi, A., et al. An accurate single-electron pump based on a highly tunable silicon quantum dot. Nano Lett. 14 (6), 3405-3411 (2014).

- Pekola, J. P., et al. Single-electron current sources: Toward a refined definition of the ampere. Rev. Mod. Phys. 85 (4), 1421-1472 (2013).

- Giblin, S. P., et al. Towards a quantum representation of the ampere using single electron pumps. Nat. Commun. 3, 930 (2012).

- Kouwenhoven, L. P., Austing, D. G., Tarucha, S. Few-electron quantum dots. Rep. Prog. Phys. 64 (6), 701-736 (2001).

- Veldhorst, M., et al. An addressable quantum dot qubit with fault-tolerant control fidelity. Nat. Nanotech. 9 (12), 981-985 (2014).

- Fujiwara, A., Nishiguchi, K., Ono, Y. Nanoampere charge pump by single-electron ratchet using silicon nanowire metal-oxide-semiconductor field-effect transistor. Appl. Phys. Lett. 92 (4), 042102-1-042102-3 (2008).

- Jehl, X., et al. Hybrid Metal-Semiconductor Electron Pump for Quantum Metrology. Phys. Rev. X. 3 (2), 021012-1-021012-7 (2013).

- Tettamanzi, G. C., Wacquez, R., Rogge, S. Charge pumping through a single donor atom. New J. Phys. 16 (6), 063036-1-063036-17 (2014).

- Koppinen, P. J., Stewart, M. D., Zimmerman, N. M. Fabrication and Electrical Characterization of Fully CMOS-Compatible Si Single-Electron Devices. IEEE Trans Electron Devices. 60 (1), 78-83 (2013).

- Fletcher, J. D., et al. Stabilization of single-electron pumps by high magnetic fields. Phys. Rev. B. 86 (15), 155311-1-155311-6 (2012).

- Kataoka, M., et al. Tunable Nonadiabatic Excitation in a Single-Electron Quantum Dot. Phys. Rev. Lett. 106 (12), 126801-1-126801-4 (2011).