Protocol

注:本协议描述用于制造,封装和测试基于硅的MOS QD技术的单电子泵的过程。在子部分1和2所讨论的步骤进行了在ISO5的洁净室,而第3在ISO6实验室中进行。环境条件被连续地控制。对于温度和湿度的标称值被设定在20±1℃和55%±5%之间。

1.微细

- 场氧化物

- 清洗晶片浸入下列:食人鱼蚀刻(10分钟),去离子(DI)水(10分钟),RCA-2溶液(DI水175毫升,盐酸30毫升,H 2 O 2的 30毫升在100℃下为10分钟),去离子水(5分钟),氢氟酸(HF)酸在水中稀释10:1(10秒),DI水(10分钟)。处理频率( 即 ,护目镜,PVC围裙,和PVC手套)时,使用防护服。继续在规定的顺序。

- 将晶圆在900℃的氧化炉和氧化步骤如下:干燥的O 2(10分钟),湿的O 2(40分钟),干O 2(10分钟),N 2(15分钟)。

- 欧姆接触

- 进行光刻和蚀刻氧化物。

- 沉积的粘合促进六甲基二硅氮烷(HMDS)几纳米厚层到晶片表面上,如下所示:预烘在热板上在110℃下1分钟,倒在玻璃烧杯中〜50毫升的HMDS,将烧杯并在真空室中的晶片,撤离和等待2分钟。

- 旋转晶片的两个前后侧上的2-4微米厚的光刻胶层(3000-5000转,在25-40秒取决于所需厚度)。

- 暴露在掩模对准紫外光(10毫瓦/厘米2,根据抗蚀剂厚度4-10秒)。在热板上在110℃下1分钟后烘焙。

- 发展1-2分钟,然后用清水冲洗用去离子水。 执行O 2等离子蚀刻20分钟(压力= 340乇;入射功率= 50瓦;反射功率<1W)。

- 在缓冲的HF酸溶液蚀刻氧化物(15:1,4-5分钟,刻蚀速率≈20纳米/分钟,在30℃)。冲洗在去离子水(5分钟)。吹干用N 2。

- 通过浸渍在丙酮中除去光致抗蚀剂。涮在异丙醇(IPA),然后吹干用N 2。

- (根据所期望的掺杂浓度的N 2流量为30-45分钟)放置晶片在炉中,在1000℃下用磷源。

- 用HF酸稀释在水(10:1,3-4分钟,蚀刻速率≈40纳米/分在30℃下)除去污染的氧化物层,冲洗去离子水(10分钟)。

- 作为氧化1.1.2。

- 进行光刻和蚀刻氧化物。

- 栅氧化层

- 重复步骤1.2.1和1.2.2。

- 放置晶片在专用炉中,在800℃和氧化步骤如下:干燥的O 2(10分钟)中,dichloroethylene + O 2(20分钟),干O 2(10-30分钟取决于所需的氧化层厚度),N 2(15分钟)。

- 欧姆接触金属化

- 重复步骤1.2.1。

- 放置晶片于电子束蒸发。蒸发的铝100nm的0.2-0.5纳米/秒和5×10 -6乇。

- 浸泡在N-甲基-2-吡咯烷酮(NMP)上加热板的晶片在80℃下1小时,以抬离金属。必要时可使用超声搅拌。冲洗在IPA 2分钟。吹干用N 2。

- 退火中形成气体,在400℃下进行至少15分钟。

2.纳米加工

- 晶片切割

- 自旋任何抗蚀剂到晶片充当保护涂层(的聚合物和纺丝参数类型无关在此阶段)。

- 使用金刚石针尖切丁酶到晶片切成〜10×2mm的2单个芯片。

- 清洁的

- 泡在NMP 1小时烤盘上,在80℃,然后用清水冲洗在IPA 2分钟。吹干用N 2。

- 执行O 2等离子蚀刻5分钟(入射功率= 50瓦;反射功率<1W)。

- 旋清洁用丙酮和IPA(7500转,30秒)

- 对准标记图案

- 自旋聚甲基丙烯酸甲酯(PMMA 950K)的A4抗蚀剂(5,000-7,500转,30秒取决于所需厚度)。典型工作厚度≈150-200纳米。烘烤的抗蚀剂在热板上在180℃下90秒。

- 开展电子束光刻。使用以下条件写:束能量= 30千电子伏,束流≈30 PA,面积剂量≈500-650μC/厘米2取决于标记的大小和厚度抵制。

- 开发中的抗蚀剂的甲基异丁基酮和IPA中的溶液(1:3)为40〜60秒,然后用清水冲洗在IPA持续20秒。吹干用N 2枪。

- 地方该芯片在电子束蒸发器。蒸发的Ti为15nm,并在0.2-0.4纳米/秒的65毫微米的Pt和5×10 -6乇。

- 取下金属如步骤1.4.3。

- 清洁芯片作为在步骤2.2.2-2.2.3。

- 门图案

- 旋抵制在2.3.1。

- 开展电子束光刻。使用以下条件写入高分辨率的特点:束能量= 30千电子伏,束流≈30 PA,面积剂量≈500-700μC/厘米2。写条件低分辨率特点:束能量= 15千电子伏,束流10≈呐,面积剂量≈400-600μC/厘米2。

- 制定抵制在2.3.3。

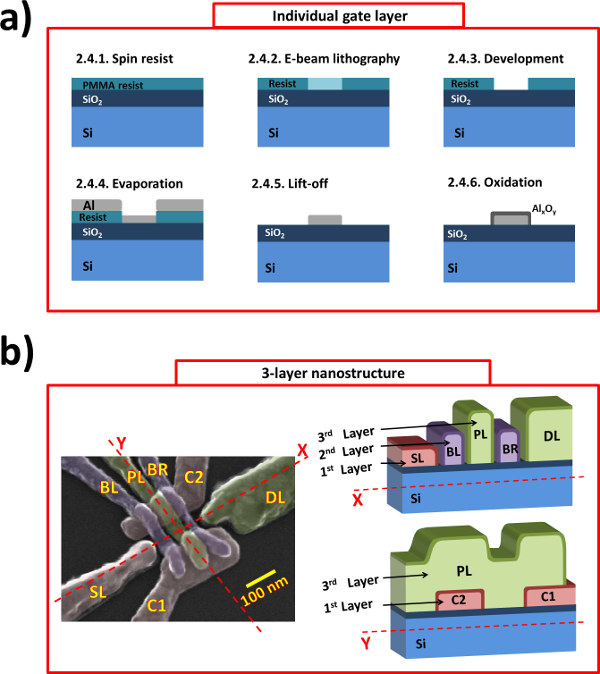

- 发生在热蒸发器芯片。蒸发的Al在0.1-0.4纳米/秒和1-9×10 -6毫巴。目标厚度相应于层号不同而不同, 如图2B(25-35毫微米为层1,45-65纳米为第2层,75-90Ñ米为3层)。

- 取下金属如步骤1.4.3。

- 在热板上进行铝氧化,在150℃下进行5-10分钟。

- 清洁片作为步骤2.2.3。

- 重复步骤2.4.1-2.4.7两次以实现3层的栅极堆叠。

3.包装设备

- 骰子芯片如在步骤2.1

- 冲洗在丙酮和IPA所得小的芯片2分钟。

- 粘上一个单件,以在印刷电路板(PCB)与聚甲基丙烯酸甲酯的A5。等待2分钟,它干。另外,为提高热化,使用银环氧树脂。

- 加载到PCB的楔形键合机并继续布线。

4.设备完整性测试

- 安装包含有线设备到浸探头的PCB。

- 接线板的电气线路的那些浸渍探针。

- 将探头插入含有液态氦的容器。缓慢进行,以避免过多的氦气b油客。

- 对于每个设备门,所述探针的相应的室温电极连接到源测量单元,同时保持接地的其它栅极。设置符合当前要少娜。扫从零电压到1.5V,步长为0.1伏,测量并记录电流。

- 各栅极线连接到电池供电的可变直流电压源,源极线到内置的交流电压源一个锁相放大器,且漏极线到锁定放大器的输入端口。

- 测量到漏极电导为不同栅电压配置( 见图4)的来源。

- 在全球范围内坡道通过保持C1和C2门应用于门BL,BR,PL,SL和DL,电压接地。记录“接通”器件的特性。

- 单独减速每个栅极电压和记录门“夹断”的特点。

- 调节栅极电压来静电定义曲antum点通过设置BL和BR(PL,SL和DL)小(较大)的电压比导通电压。记录库仑阻塞特性。

Representative Results

设备制造

初始微制造工艺(议定书子部分1)是商业4英寸高纯度硅晶片上进行(n型掺杂浓度≈10 12 cm -3的;电阻率> 10kΩcm;厚度= 310-340微米)。这样做的目的是实现在其上的栅电极将被沉积在基板上。该基板是由封端的场氧化(步骤1.1),封端的场氧化(步骤1.2),覆盖有高质量的栅极氧化物(步骤1.3)的本征区域的n +区域的本征区域的,和金属化的n +区域欧姆接触(步骤1.4)。 图1A-D示出了微细加工的主要步骤。 图1E示出了一个基片场的显微镜图像的微细加工之后。最小特征尺寸的光刻在此阶段是约4微米。

串口在步骤1.1生长2氧化物层具有100nm的标称厚度,并且被用作钝化层。充当欧姆导体的n型区经由磷扩散获得。目标掺杂浓度是大约10月19日至 10月20日 cm -3以下 。高质量的SiO 2,其选择生长用作栅极电介质具有5纳米的标称厚度。目标接口缺陷密度是<10 10电子伏特-1 cm -2的在中间能隙。专用和内置特意墙三重炉用于此过程。这个系统被设计成最小化从重金属离子和移动的碱金属离子污染,以及防止水分扩散进入氧化室。为了形成电接触,铝焊盘通过电子束蒸发在n型区的部分沉积。

该纳米制造工艺(见分节2)芯片上执行SUBSTR通过切割在第1步的目的处理的晶片获得的茨是实现用于静电限定该MOS量子点纳米尺度栅电极。每个纳米加工运行通常会产生10-15完整的设备样品。扫描电子显微照片(SEM),每批次成像的1-2设备通常进行,以确认该EBL光刻阶段获得了成功。自扫描电镜成像可注入电荷在衬底或在金属栅极而造成泄漏,仅一小数量的设备进行检查以这种方式,而其余的电测试。最小特征尺寸的光刻在此阶段是约35纳米。以实现沉积Al膜的均匀性好,该金属被蒸发速率为几个埃/秒的速度慢,而在基片被安装在一个旋转台。这被保持在RT,并且在Al晶粒尺寸估计为约20nm。 图2A示出了nanofabricatio的主要步骤Ñ 过程。 图2B示出与该栅电极的正确定义被验证的SEM图像。一般来说,人们的目的是实现这些门直接定义QD(BL,BR和PL)用尽可能小的特征尺寸。与此相反,用于定义电子储层(DL和SL)这些门可以有更大的尺寸,以避免能量水平中的引线的无意离散。实现了在步骤2.3纳米尺度的Ti / Pt的标记被用作栅极的三个层的一致对准参考。铂是选择了其相对于优秀的对比度,以在SiO 2表面的电子束。钛是用于提高粘合性。

在制造过程的各个阶段,碳纤维尖镊子用于处理芯片,以减少破坏性静电放电(ESD)的可能性。

最后,为了进行上INDIVI电测量双重装置,每个芯片需要在更小的碎片为约2×2mm的2(子部分3)被切割。然后每一块胶合到一个特制的PCB(罗杰斯R03010低损耗介质),其销通过铝导线被连接到器件电极。引线键合是用一个楔形键合机机不加热的芯片。合适的键合参数的选择是基于两方面的考虑。一方面,所述引线接合需要穿孔的热的Al Y 2 O x层和使良好的金属对金属与栅极焊盘接触。另一方面,过大的机械应力可能导致的冲头槽式事件,这损害了场氧化物的栅极和原因衬底泄漏下方。在布线过程中,使用防静电手环的建议,以防止静电放电。在图3中 ,有6个单独的设备将芯片粘接到印刷电路板。

器件的完整性测试

之前Ë加载装置插入mK的温度测量平台如稀释制冷机,初步电测试在4.2K下进行检查样品的完整性(参见议定书子部分4)。为此,在PCB插入到无氧铜外壳和安装到一浸探针,其最终被浸入液态He。

初始测试通常为在各个闸门顺序执行泄漏测试。源测量单元被连接到一个单独的栅电极,而其他人都接地。电压上升到1.5 V和电流的测量在源头。在该电压范围内,在正常的门是不应该进行,因为SiO 2层从硅衬底隔离的金属和Alÿ○×绝缘重叠栅极。典型地,氧化物击穿已知会出现对电压高于〜为4V较大,这取决于设备的几何形状和氧化物THIC到天堂。因此,如果在测试过程中检测到的电流,则很可能在氧化层中的至少一个已损坏,该设备具有被丢弃。通常,门的小于10%的显示泄漏。产率是已知的受栅电极的平面延伸。特别是,与栅氧化物区域就越有可能将具有栅极 - 基片的泄漏的栅极的较大的重叠。类似地,来自不同层的栅极的栅极到栅极泄漏的更可能发生之间的较大的重叠会。引用的产量相关占据约50μm2的面积上的薄氧化物栅和与层间的大约0.5微米2重叠。

一旦设备已通过初始泄漏测试时,源极和漏极触点连接到一个锁定放大器和栅极到模块化可控电压电池架。在此配置中,该装置被接通öN以全球同步斜坡所有的栅极电压。接着,将各栅极电压分别逐渐减小,同时保持其他在高电压,以验证个人门的夹断电流的能力。 图4A示出了这些测量的代表痕迹。由于没有任何一个源 - 漏传导通路或个别栅极夹断是经常一些类型的门损坏诸如栅极爆炸或金属不连续的指示。

最后,源-漏电流被测量为源-漏偏压和柱塞栅极电压的函数来观察库仑阻塞16(参照图4B)的签名。

测量

一旦合适的设备已被发现,它是从液态He容器中取出,并用一个热风枪干燥,以避免形成湿气可能引起静电。最后,它被转移到一个稀释制冷机。

<P类=“jove_content”>该实验是在自制塑料稀释制冷机进行约100 m·K的基础温度。低温恒温器是在真空室中浸渍在4.2K下氦浴。电线被热能化在1K池也被用来冷凝传入的3He蒸气。在混合室,从所述的3He富相入氦3-稀相的3He原子的吸热转移允许系统以达到约100 m·K的基础温度。如图5所示 ,冰箱装有20直流线路和用于连接的室温电子给设备在低温下3射频线。五个直流线路是Thermocoax电缆和15双绞线织机导线。这些线连接样本到电池供电的直流电压源的栅电极。分压器在RT用于减少对个别栅极电噪声。射频线是半刚性同轴电缆是在4K衰减10 dB至减少热噪声和直流阻塞在室温。这些线连接到PCB上的偏置T形件的共面波导。

低噪声跨导放大器和一个数字万用表用于测量由泵产生的电流。电子经由电池供电的光隔离器连接到设备,以防止接地回路的形成。射频驱动信号由任意波形发生器,其接地从低温恒温器通过一个直流嵌段成分之一分离出产生的( 见图5)。

在PCB包含16纯直流线路和用于直流和交流电压结合在低温4偏置T形线路。 如图3B所示 ,RC分立元件用于实现三通连接(R = 100千欧,C = 10 nF的),50Ω匹配集成共面波导用于高频信号的传输。

e_content“>一旦该装置是在mK的温度,栅极电压被调整,使得在QD单电子占用为止。特别是,隧道壁垒下门的BL和BR形成,并且下栅极的电子积聚层被诱导PL,SL和DL。为此,阻挡栅极电压被设置为低于其导通的值,而积累栅极被极化在一个大于-导通电压,在这种方式的QD是下栅极PL所形成和它的平面延伸通过门电路C1和C2的电压被保持在低于其导通的值以诱导静电约束控制。接着,对射频信号导通,以周期性地调节所述隧道势垒(多个)的透明度,以及电化学点的电位。单电子泵送实现与一个或两个正弦驱动电压。在一个信号驱动的情况下,驱动信号被施加到栅极的BL以调制隧道势垒的电势在左手中机端量子点。在两信号驱动的情况下,交流激励被施加到栅极的BL和PL调节两者的左屏障和QD的电位在相同的频率但具有不同相位和幅度。这些附加自由度允许一个用于控制电子转移13的方向。一个迭代过程通常需要调整的主要实验参数( 即 ,射频驱动信号振幅/相位和直流栅极电压),并达到最佳当前量化。注意的是,无论这两个泵送协议需要一个漏源偏压来执行电荷转移。因此,在源电极和漏电极在泵操作期间接地。 图6示出了特性的电流plateaux在EF的通过施加两信号正弦驱动到输入屏障(BL)和柱塞(PL)栅极获得的整数倍。这些数据取自在相对低的驱动频率(10兆赫)的量,吨参数uning可以快速进行。在实践中,理想的是操作泵在数百MHz,通常需要更精细的参数优化13。

图1.微细加工。(一 )示意图的微细加工主要步骤图。漫画并非按比例绘制。 (B)中实现的掺杂区的欧姆接触。 (C)栅氧化层的实现。 (D)的金属化的欧姆接触。 ( 五)微观个体领域的微细加工后,在一个芯片上的图像就完成了。现场尺寸为1.2×1.2 平方毫米。 请点击此处查看该图的放大版本。

图2纳米加工。(A)的制造方法,各个栅层。漫画并非按比例绘制。 (B)中用于电荷泵浦实验的3层栅极纳米结构。左:类似于用于测量所述一个设备的SEM图像。右:在整个X切割和Y切割设备的示意性的横截面图请点击此处查看该图的放大版本。

图3.电气连接到样品。在印刷电路板(A)布局。 (B)中的印刷电路板与一个偏置T形(左)的区域的放大的ð等效电路(右)。 (C)上形成芯片粘在芯片保持器和连结线,供与PCB电连接6的各个字段。 (D)纳米加工后,单个字段的显微图像。在栅氧化层区域的中心门布局(E)的SEM图像。 请点击此处查看该图的放大版本。

图4.初步试验。(A)的源-漏交流电流(均方根),为不同的栅极电压的函数。迹线在113.17赫兹测量与锁定放大器50μV 有效值激励。对于个别栅极电压迹线的其余的栅极电压被固定为2.0伏,除了当V C1 = <的EM> V C2 =源-漏电流的0.0 V.(B)的彩色图作为柱塞栅极电压和源极-漏极偏置电压:V SL的函数= 1.5,V DL = 1.15,V BL = 0.78伏, V BR = 0.85,V C1 = V C2 = 0.0 V. 请点击此处查看该图的放大版本。

图5.示意图测量的设置。二直流线(绿色)和三个同轴射频线(黑)连接的RT电子到PCB。泵(紫色)的漏极被连接到跨导放大器和通过光隔离器的数字万用表,而源极接触(红色)接地。单独的接地连接(我ndicated用不同的符号)被用于电子仪器和低温恒温器的电线。 请点击此处查看该图的放大版本。

图6.当前量化。在应用到门BL和PL F = 10 MHz的泵浦电流为第 V PL功能的双信号正弦波驱动。相位差= 49度,V RF PL = V RF BL = 0.31 V峰峰值。抽plateaux在EF的整数倍的理想位置显示为红色水平线。 请点击此处查看该图的放大版本。

Discussion

本文报道的协议描述的技术来制造硅的MOS量子点,以及实验步骤,以测试它们的功能完整性和操作它们作为单电子泵。值得注意的是,通过调整栅设计,在同一个制造工序,可以采用,以产生设备适合于量子位的读出和控制17,以及电荷抽12,13。我们注意到,许多在本文中所引述的工艺参数可以根据所使用的制造工具而变化(校准,使或模型),以及在硅基板(厚度和背景掺杂浓度)的类型。量如光刻曝光剂量或开发时间,蚀刻或氧化的持续时间,必须仔细校准和测试,以确保可靠的产率。此外,关键的是要避免因使用不同的过程相同的制造工具所产生的交叉污染。为此,一些铬的itical步骤进行的设备专用于硅处理,如金属蒸发器,氧气转炉和HF浴。

更一般地,硅被绘制一个越来越大的兴趣作为首选材料来实现电荷泵18-20。这部分是由于使用的是工业兼容的硅工艺实现了新的基于量子的电流标准的吸引力角度。这将受益于成熟的,可靠的集成技术的可扩展性,并行和驾驶开销。重要的是,一个完整的互补MOS(CMOS)技术,无传统的金属作为栅极材料,已经显示出大大降低背景电荷波动单电子器件21。这种波动可以实现计量精度有害的。

这里所讨论的协议被限制为实现MOS纳米器件与金属栅极。因此,为了achie已经充分工业兼容性和减少电荷的波动,这将需要修改的栅极沉积技术,并使用高度掺杂的多晶硅作为栅极材料。

总之,这里所讨论的MOS QD泵最近结合硅的技术优势,在精确的电流产生13方面是非常好的性能。这源于设计和制造方法,该方法允许一个堆叠多个栅层导致紧凑和灵活的系统的高的灵活性。与减少的背景电荷波动的潜在点起来的静电禁闭得到的细调谐设置了舞台,以克服在其他半导体中观察到的主要挑战泵22,23。

Disclosures

作者什么都没有透露。

Acknowledgments

我们感谢KY谭P.见和GC Tettamanzi进行了有益的讨论。我们承认,从澳大利亚研究理事会(批准号:DP120104710),芬兰科学院(批准号:251748,135794,272806)的资金支持,并支持澳大利亚国家制造工厂的设备制造。 AR确认来自新南威尔士大学的早期职业研究员补助金计划的资金支持。设施和技术支持由阿尔托大学在纳米加工Micronova中心规定也承认。

Materials

| Name | Company | Catalog Number | Comments |

| Silicon wafers | TOPSIL | 4 inch | |

| Electron-beam lithography machine | Raith gmbh | Raith 150two | |

| E-beam resist | MicroChem gmbh | PMMA | |

| Photoresist | MicroChem gmbh | nLOF2020 | |

| Mask aligner | Quintel | Q6000 | |

| Photoresist developer | MicroChem gmbh | AZ826MIF |

References

- Sze, S. M. Physics of Semiconductor Devices. , Wiley. Interscience, NY. 505-566 (1969).

- Moore, G. E. Cramming More Components onto Integrated Circuits. Electronics. 38, 114-117 (1965).

- Voisin, B., et al. Few-Electron Edge-State Quantum Dots in a Silicon Nanowire Field-Effect Transistor. Nano Lett. 14 (4), 2094-2098 (2014).

- Asenov, A., Brown, A. R., Davies, J. H., Savas, K., Slavcheva, G. Simulation of Instrinsic Parameter Fluctuations in Decananometer and Nanometer-Scale MOSFETs. IEEE Trans Electron Devices. 50 (9), 1837-1852 (2003).

- Zwanenburg, F. A., et al. Silicon Quantum Electronics. Rev. Mod. Phys. 85 (3), 961-1019 (2013).

- Ladd, T. D., et al. Quantum computers. Nature. 464 (7285), 45-53 (2010).

- Piquemal, F. Genevès, G. for a direct realization of the quantum metrological triangle. Metrologia. 37 (3), 207-211 (2000).

- Angus, S. J., Ferguson, A. J., Dzurak, A. S., Clark, R. G. Gate-Defined Quantum Dots in Intrinsic Silicon. Nano Lett. 7 (7), 2051-2055 (2007).

- Gonzalez-Zalba, M. F., Heiss, D., Podd, G., Ferguson, A. J. Tunable aluminium-gated single electron transistor on a doped silicon-on-insulator etched nanowire. Appl. Phys. Lett. 101 (10), 103504-103501 (2014).

- Lim, W. H., et al. Observation of the single-electron regime in a highly tunable silicon quantum dot. Appl. Phys. Lett. 95 (24), 242102-242103 (2009).

- Yang, C. H., et al. Spin-valley lifetimes in silicon quantum dots with tunable valley splitting. Nat. Commun. 4 (2069), (2013).

- Chan, K. W., et al. Single-electron shuttle based on a silicon quantum dot. Appl. Phys. Lett. 98 (21), 212103-212101 (2011).

- Rossi, A., et al. An accurate single-electron pump based on a highly tunable silicon quantum dot. Nano Lett. 14 (6), 3405-3411 (2014).

- Pekola, J. P., et al. Single-electron current sources: Toward a refined definition of the ampere. Rev. Mod. Phys. 85 (4), 1421-1472 (2013).

- Giblin, S. P., et al. Towards a quantum representation of the ampere using single electron pumps. Nat. Commun. 3, 930 (2012).

- Kouwenhoven, L. P., Austing, D. G., Tarucha, S. Few-electron quantum dots. Rep. Prog. Phys. 64 (6), 701-736 (2001).

- Veldhorst, M., et al. An addressable quantum dot qubit with fault-tolerant control fidelity. Nat. Nanotech. 9 (12), 981-985 (2014).

- Fujiwara, A., Nishiguchi, K., Ono, Y. Nanoampere charge pump by single-electron ratchet using silicon nanowire metal-oxide-semiconductor field-effect transistor. Appl. Phys. Lett. 92 (4), 042102-1-042102-3 (2008).

- Jehl, X., et al. Hybrid Metal-Semiconductor Electron Pump for Quantum Metrology. Phys. Rev. X. 3 (2), 021012-1-021012-7 (2013).

- Tettamanzi, G. C., Wacquez, R., Rogge, S. Charge pumping through a single donor atom. New J. Phys. 16 (6), 063036-1-063036-17 (2014).

- Koppinen, P. J., Stewart, M. D., Zimmerman, N. M. Fabrication and Electrical Characterization of Fully CMOS-Compatible Si Single-Electron Devices. IEEE Trans Electron Devices. 60 (1), 78-83 (2013).

- Fletcher, J. D., et al. Stabilization of single-electron pumps by high magnetic fields. Phys. Rev. B. 86 (15), 155311-1-155311-6 (2012).

- Kataoka, M., et al. Tunable Nonadiabatic Excitation in a Single-Electron Quantum Dot. Phys. Rev. Lett. 106 (12), 126801-1-126801-4 (2011).