Protocol

Nota: Este protocolo descreve os procedimentos utilizados para fabricar, embalar e testar bombas elétrons único baseado em silício tecnologia MOS QD. Os passos discutidos em sub-seções 1 e 2 são realizadas em uma sala limpa ISO5, enquanto aqueles da seção 3 são realizados em laboratórios ISO6. As condições ambientais são controlados de forma contínua. Valores nominais de temperatura e humidade são definidas a 20 ± 1 ° C e 55% ± 5%, respectivamente.

1. Microfabrication

- Óxido de campo

- Limpar a bolacha por imersão no seguinte: etch piranha (10 min), água desionizada (DI) de água (10 min), 2-RCA solução de água Dl (175 ml, 30 ml de HCl, H 2 O 2 30 mL a 100 ° C durante 10 min), água desionizada (5 min), fluorídrico HF) ácido (diluído em água 10: 1 (10 seg), água Dl (10 min). Use vestuário de protecção ao manusear HF (ou seja, óculos de proteção, avental de PVC e luvas de PVC). Proceder pela ordem indicada.

- Coloque a bolachaem forno de oxidação a 900 ° C e oxidar em etapas como se segue: O seco 2 (10 min), molhado O 2 (40 min), 2 O seco (10 min), 2 N (15 min).

- Ôhmicas Contactos

- Realizar fotolitografia e óxido de etch.

- Depositar uma camada-poucos-nm de espessura de promotor de adesão de hexametildissilazano (HMDS) na superfie da bolacha da seguinte forma: Pré-coze numa placa de aquecimento a 110 ° C durante 1 min, verter ~ 50 ml de HMDS em um copo de vidro, colocar o copo e a bolacha na câmara de vácuo, evacuar e esperar durante 2 min.

- Girar uma camada de 2-4 mícrons de espessura de material fotosensitivo sobre ambos os lados da frente e traseira da pastilha (3.000-5.000 rpm, 25-40 seg dependendo da espessura desejada).

- Expor à luz ultra-violeta em alinhador de máscara (10 mW / cm 2 para 4-10 sec acordo para resistir espessura). Pós-cozer numa placa de aquecimento a 110 ° C durante 1 min.

- Desenvolver para 1-2 min, em seguida, enxágüe em água deionizada. Execute O etch 2 plasma durante 20 minutos (pressão = 340 mTorr; potência incidente = 50 W; refletido energia <1 W).

- Óxido Etch em solução tamponada com ácido HF (15: 1, 4-5 min, taxa de etch ≈ 20 nm / min a 30 ° C). Lavar em água desionizada (5 min). Seque com N2.

- Remover fotorresistente por imersão em acetona. Enxágüe em isopropanol (IPA), em seguida, seque com N2.

- Coloque bolacha no forno a 1000 ° C com a fonte de fósforo (fluxo de N2 durante 30-45 min, dependendo da densidade desejada dopagem).

- Remover a camada de óxido contaminado com ácido HF diluído em água (10: 1, 3-4 min, taxa de corrosão ≈ 40 nm / min a 30 ° C), enxaguar em água desionizada (10 min).

- Oxidar como em 1.1.2.

- Realizar fotolitografia e óxido de etch.

- Portão Oxide

- Repita os passos 1.2.1 e 1.2.2.

- Coloque bolacha em forno a 800 ° dedicado C e oxidar em etapas como se segue: O seco 2 (10 min), dichloroethylene + O 2 (20 min), 2 O seco (10-30 min, dependendo da espessura desejada de óxido), N 2 (15 min).

- Ôhmicas Contatos Metalização

- Repita o passo 1.2.1.

- Coloque wafer no evaporador por feixe de elétrons. Evaporar 100 nm de alumínio a 0,2-0,5 nm / seg e 5 x 10 -6 Torr.

- Soak a bolacha em N-metil-2-pirrolidona (NMP) na placa de aquecimento a 80 ° C durante 1 hora para retirar o metal. Usar agitação ultra-sónica, se necessário. Enxágüe em IPA por 2 min. Seque com N2.

- Hibridação em gás de formação a 400 ° C durante pelo menos 15 min.

2. Nanofabricação

- Wafer corte em cubos

- Girar em qualquer resistir a bolacha para actuar como revestimento protector (tipo de parâmetros de fiação e de polímero são irrelevantes, nesta fase).

- Use diamante ponta dicer para cortar o wafer em chips individuais de ~ 10 x 2 mm2.

- Limpeza

- Mergulhe em NMP durante 1 hora em placa a 80 ° C, e depois enxaguar em IPA por 2 min. Seque com N2.

- Execute O etch 2 plasma por 5 min (potência incidente = 50 W; refletido poder <1 W).

- Gire limpo com acetona e IPA (7.500 rpm, 30 seg)

- Marcadores de alinhamento padronização

- Rotação polimetil metacrilato (PMMA 950k) A4 resistir (5,000-7,500 rpm, 30 segundos, dependendo da espessura desejada). Espessura de trabalho típico ≈ 150-200 nm. Cozer a resistir numa placa de aquecimento a 180 ° C durante 90 seg.

- Realizar litografia por feixe de elétrons. Use as seguintes condições de gravação: energia do feixe = 30 keV, a corrente do feixe ≈ 30 Pa, a dose área ≈ 500-650 uC / cm 2, dependendo do tamanho marcadores e resistir espessura.

- Desenvolver a resistir em uma solução de metil-isobutil-cetona e IPA (1: 3) para 40-60 segundos, depois enxaguar em IPA durante 20 seg. Seque com N 2 arma.

- Lugaro chip no evaporador por feixe de elétrons. Evaporar 15 nm de Ti e 65 nm de Pt a 0,2-0,4 nm / seg e 5 x 10 -6 Torr.

- Levante o metal como na etapa 1.4.3.

- Limpe chip como nos passos 2.2.2-2.2.3.

- Portão padronização

- Spin resistir como em 2.3.1.

- Realizar litografia por feixe de elétrons. Use as seguintes condições de gravação para recursos de alta resolução: energia do feixe = 30 keV, a corrente do feixe ≈ 30 Pa, a dose área ≈ 500-700 uC / cm 2. Escrever condições para características de baixa resolução: energia do feixe = 15 keV, a corrente do feixe ≈ 10 nA, a dose área ≈ 400-600 uC / cm 2.

- Desenvolver a resistir como em 2.3.3.

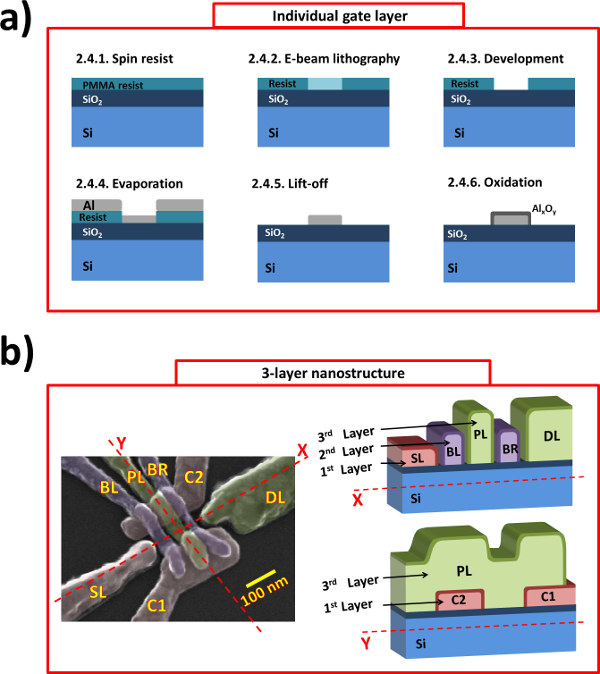

- Inserir o chip no evaporador térmico. Evaporar em Al 0,1-0,4 nm / seg e 1-9 x 10 -6 mbar. Alvo espessura varia de acordo com o número de camada, como mostrado na Figura 2B (25-35 nm para a camada 1, 45-65 nm para a camada 2, 75-90 nm para Layer 3).

- Levante o metal como na etapa 1.4.3.

- Realizar Al oxidação numa placa de aquecimento a 150 ° C durante 5-10 min.

- Limpe chip como no passo 2.2.3.

- Repetir passos 2.4.1-2.4.7 duas vezes para realizar a estrutura de porta 3-camada.

Embalagem 3. Dispositivo

- Chip de dados como no passo 2.1

- Lavar os chips menores resultantes em acetona e IPA por 2 min.

- Cole uma peça individual de uma placa de circuito impresso (PCB), com PMMA A5. Espera 2 minutos para secar. Alternativamente, para aumentar a estabilização térmica, usar prata epóxi.

- Carregue o PCB para um bonder cunha e prosseguir com a fiação.

4. testes integridade do dispositivo

- Monte o PCB que contém o dispositivo com fio para uma sonda de mergulho.

- Conectar as linhas eléctricas do PCB às da sonda de mergulho.

- Inserir a sonda em um recipiente contendo hélio líquido. Prossiga lentamente para evitar excesso de hélio bóleo-off.

- Para cada porta do dispositivo, ligue o eléctrodo de temperatura ambiente correspondente da sonda a uma unidade de fonte medida, mantendo as outras portas aterrados. Ajuste a corrente de conformidade para alguns nA. Varrer a tensão de zero a 1,5 V em intervalos de 0,1 V, medir e registrar a corrente.

- Conecte cada linha de porta a uma fonte de tensão CC variável alimentado por bateria, a linha de origem para o built-in fonte de tensão ac de um amplificador lock-in, ea linha de dreno para a porta de entrada do amplificador lock-in.

- Medir a fonte para o dreno condutância de diferentes configurações de tensão da porta (ver Figura 4).

- Globalmente rampa até as voltagens aplicadas aos portões BL, BR, PL, SL e DL, mantendo C1 e C2 portões aterrada. Grave as características "turn-on" do dispositivo.

- Individualmente cada rampa de tensão portão e gravar características dos portões 'pinch-off'.

- Ajuste as tensões de porta para definir electrostaticamente um qudot antum definindo as tensões sobre BL e BR (PL, SL e DL) menor (maior) do que o turn-on tensões. Grave as características do bloqueio de Coulomb.

Representative Results

Fabricação de dispositivos

O processo de microfabricação inicial (sub-secção 1 do Protocolo) é realizada em um comercial de 4 polegadas de alta pureza wafer de silício (n-tipo de concentração doping ≈ 10 12 cm -3; resistividade> 10 kΩcm; espessura = 310-340 mm ). O objectivo é o de realizar o substrato sobre o qual os eléctrodos de porta irá ser depositado. Este substrato é feito de uma região intrínseca cobertas com óxido de campo (passo 1.1), um n + região nivelada com óxido de campo (passo 1.2), uma região intrínseca cobertas com óxido de porta de alta qualidade (passo 1.3), e um metalizado n + região para contactos óhmicos (passo 1.4). As Figuras 1A-D ilustram as principais etapas do processo de microfabricação. A Figura 1E mostra uma imagem microscópica de um campo substrato após microfabricação. O tamanho mínimo de característica para o litografia nesta fase é de aproximadamente 4 um.

O SiO2 camada de óxido cultivadas no passo 1.1 tem uma espessura nominal de 100 nm e é utilizado como uma camada de passivação. As regiões do tipo n, que actuam como condutores óhmicos são obtidos através de difusão de fósforo. A densidade de doping alvo é de aproximadamente 19 outubro - 20 outubro cm -3. A alta qualidade de SiO 2, o qual é cultivado selectivamente para ser utilizado como porta dieléctrico tem uma espessura nominal de 5 nm. A densidade de defeitos de interface alvo é <10 10 eV -1 cm -2 ao meio-gap. Um forno dedicado e propositadamente construído muro triplo é usado para este processo. Este sistema foi concebido para minimizar a contaminação de iões de metais pesados e iões alcalinos móveis, assim como evitar que a humidade se difunda para a câmara de oxidação. De modo a formar os contactos eléctricos, almofadas de alumínio são depositados por meio de evaporação por feixe de electrões sobre uma parte das regiões do tipo n.

O processo de nanofabricação (ver sub-secção 2) é realizada no chip substrates obtidos por cortar a bolacha processado no passo 1. O objectivo é o de realizar os eléctrodos de porta nano-escala usada para definir os electrostaticamente QDs MOS. Cada execução nanofabricação produz tipicamente 10-15 amostras de dispositivos completos. Micrografia de varrimento electrónico (SEM) de imagens de dispositivos de 1-2 por lote é normalmente realizada para confirmar que as fases de litografia EBL têm sido bem sucedidas. Desde SEM imagem pode injetar acusações no substrato ou nas portas metálicas e causar vazamentos, apenas um pequeno número de dispositivos é verificada, desta forma, enquanto o resto é eletricamente testado. Tamanho mínimo de recurso para a litografia, nesta fase, é de aproximadamente 35 nm. Para obter uma boa uniformidade dos filmes depositados Al, o metal é evaporado a taxas tão lenta quanto alguns angstroms / segundo, enquanto que o substrato é montado em uma fase de rotação. Esta é mantida à temperatura ambiente, e o tamanho de grão Al é estimada como sendo de cerca de 20 nm. A Figura 2A ilustra as principais etapas do nanofabricatioprocesso n. Figura 2B mostra uma imagem SEM com a qual a definição correta dos eletrodos de porta é verificada. Em geral, visa realizar esses portões que definem directamente o QD (BL, BR e PL), com o tamanho menor recurso possível. Em contraste, aqueles portões utilizados para definir os reservatórios de elétrons (DL e SL) pode ter dimensões maiores para evitar a discretização não intencional de níveis de energia nas ligações. Os nano-escala marcadores Ti / PT realizados no passo 2.3 são utilizados como referência para o alinhamento consistente das três camadas de portões. A platina é escolhido pela sua excelente contraste com respeito à superfície de SiO2 no feixe electrónico. O titânio é usado para aumentar a adesão.

Em todas as fases do processo de fabrico, uma pinça de fibra de ponta de carbono são usadas para lidar com as aparas, de modo a reduzir o risco de uma descarga electrostática destrutiva (ESD).

Finalmente, a fim de efectuar as medições eléctricas sobre individispositivos duplos, cada pastilha tem de ser clivada em pedaços mais pequenos de cerca de 2 x 2 mm2 (sub-secção 3). Cada peça é então colada a uma PCB feito por encomenda (Rogers R03010 de baixa perda dielétrica) cujos pinos são conectados aos eléctrodos do dispositivo por meio de fios de Al. Fio de ligação é levada a cabo com uma máquina Bonder cunha sem aquecer as batatas fritas. A escolha dos parâmetros adequados de ligação baseia-se em duas considerações. Por um lado, o vínculo fio precisa perfurar o Al y O x camada térmica e fazer um bom contato metal-metal com a almofada portão. Por outro lado, um estresse mecânico excessivo pode resultar num evento que prejudica o campo de óxido por debaixo da porta e causar fugas de substrato-soco da calha. Durante o processo de fiação, a utilização de uma pulseira antiestática é aconselhável evitar a ESD. Na Figura 3, um chip com dispositivos individuais 6 é colada sobre o PCB.

Testes de integridade do dispositivo

Before carregamento de um dispositivo em uma plataforma de medição de temperatura mK, como uma geladeira diluição, testes elétricos preliminares são realizadas a 4,2 K para verificar a integridade da amostra (ver sub-secção 4 do protocolo). Para este fim, o PCB é inserida num invólucro de cobre isento de oxigénio e está montado sobre uma sonda de imersão, o qual é, eventualmente, imerso no líquido Ele.

O teste inicial é tipicamente um teste de vazamento que é realizada sequencialmente em cada portão. A unidade de fonte medida está conectado a um eletrodo de porta individuais, enquanto os outros são aterrados. A voltagem é aumentada para 1,5 V e a corrente é medida na fonte. Dentro desta gama de tensão, um portão funcionar correctamente não é suposto conduzir, porque a camada de SiO2 isola o metal a partir do substrato de silício e Al y O x isola portões que se sobrepõem. Tipicamente, o óxido de repartição é conhecido por ocorrer por tensões maiores que ~ 4 V, dependendo da geometria do dispositivo e de óxido thickness. Portanto, se a corrente for detectada no decurso do ensaio, é provável que pelo menos uma das camadas de óxido está danificado e o dispositivo tem de ser descartado. Usualmente, menos de 10% das portas mostram fugas. O rendimento é conhecida por ser afectada pela extensão planar dos eléctrodos de porta. Em particular, quanto maior for a sobreposição das portas com a região do óxido de porta o mais provável será ter porta-substrato fugas. De igual modo, quanto maior for a sobreposição entre as portas de diferentes camadas mais provável a ocorrência de porta-a-porta fugas será. O rendimento citado é relevante para portas que ocupam uma área de cerca de 50 mm 2 na fina de óxido e se sobrepõe com intercalar de aproximadamente 0,5 m 2.

Uma vez que o dispositivo passou no teste de vazamento inicial, os contatos fonte e dreno são conectados a um amplificador lock-in e dos portões para um rack modular bateria controlável tensão. Nesta configuração, o dispositivo está ligado on por globalmente elevando todas as tensões de porta simultaneamente. Em seguida, cada tensão da porta é aumentada separadamente para baixo, mantendo os outros em altas voltagens para verificar a capacidade de portas individuais para beliscar fora a corrente. A Figura 4A mostra traços representativos dessas medições. A ausência de qualquer um via de condução fonte-dreno ou indivíduo portão pinch-off é muitas vezes uma indicação de algum tipo de dano, como explosão portão portão de metal ou descontinuidade.

Finalmente, a corrente de fonte-dreno é medida como uma função da polarização fonte-dreno e tensão da porta êmbolo para observar a assinatura de Coulomb bloqueio 16 (ver Figura 4B).

Medições

Uma vez que um dispositivo adequado foi encontrado, que é removido do vaso Ele líquido, e seca-se com uma pistola de ar quente para evitar a formação de humidade que pode causar ESD. Finalmente, ele é transferido para um refrigerador de diluição.

<p class = "jove_content"> Os experimentos são realizados em um refrigerador de diluição plástico self-made com uma temperatura base de cerca de 100 mK. O criostato é numa câmara de vácuo imerso num banho de 4,2 K hélio. As linhas eléctricas são termalizados no pote 1 K, que também é empregado para condensar o vapor 3He de entrada. Na câmara de mistura, a transferência de átomos de 3He endotérmico da fase 3He-rico em fase 3He-diluído permite que o sistema atinja uma temperatura de base de cerca de 100 mK.Como mostrado na Figura 5, o refrigerador está equipado com 20 linhas de corrente contínua e três linhas de RF utilizadas para ligar os componentes electrónicos sala de temperatura para o dispositivo a uma temperatura baixa. Cinco das linhas de corrente contínua são cabos Thermocoax e 15 são torcidos fios do tear par. Estas linhas ligam os eléctrodos de porta da amostra a fontes de tensão dc movidos a bateria. Divisores de tensão na RT são usados para reduzir o ruído elétrico no portões individuais. As linhas de RF são cabos coaxiais, que são semi-rígidas atenuada de 10 dB a 4 K para reduzir o ruído térmico e DC bloqueados à TA. Estas linhas são ligadas aos guias de ondas coplanares dos T de polarização no PCB.

Um amplificador de transimpedância de baixo ruído e um multímetro digital são utilizados para medir a corrente gerada pela bomba. A electrónica está ligado ao dispositivo através Optoisolators alimentados por bateria para evitar a formação de circuitos de terra. Os sinais de accionamento de RF são produzidos por um gerador de forma de onda arbitrária, cuja ligação à terra é isolada a partir do uma do criostato através de um componente de bloqueio DC (ver Figura 5).

O PCB contém 16 linhas de corrente contínua puros e 4 linhas diagonais t utilizados para combinar DC e AC tensões a baixa temperatura. Tal como mostrado na Figura 3B, RC componentes discretos são utilizadas para realizar a ligação em T (R = 100 kQ, C = 10 nF), e 50 Ω-matched guias de onda coplanares integrados são utilizados para a propagação de sinais de alta frequência.

e_content "> Uma vez que o dispositivo é mK à temperatura, as tensões de porta estão ajustadas de modo que a ocupação de electrões único no QD é atingido. Em particular, barreiras de túnel são formados sob portas BL e BR, e uma camada de acumulação de electrões é induzida sob portões PL, SL e DL. Para o efeito, as tensões de porta barreira estão situados abaixo do seu turn-em valores, enquanto os portões de acumulação são polarizados a uma maior-que-turn-on tensão. Desta forma, um QD é formado sob portão PL e a sua extensão planar é controlada através de portões C1 e C2 cuja tensões são mantidas abaixo da sua tara valores para induzir o confinamento electrostático. Em seguida, os sinais de RF são ligado para modular periodicamente a transparência da barreira (s) do túnel, e a electroquimica potencial do ponto. bombeamento de electrões único é conseguido com uma ou duas tensões sinusoidais de condução. No caso de uma unidade de sinais, o sinal de accionamento é aplicado a porta BL para modular o potencial da barreira de túnel na mão esquerda -ladoa QD. No caso de a unidade de dois sinais, os ac excitações são aplicados às portas BL e PL para modular os potenciais de ambos a barreira à esquerda e o QD com a mesma frequência mas com fases diferentes e amplitudes. Estes graus de liberdade adicionais permitem controlar a direcção da transferência de electrões 13. Um processo iterativo é normalmente necessário para ajustar os principais parâmetros experimentais (ou seja, amplitudes de sinal unidade rf / fases e tensões dc Gate) e alcançar quantização atual ideal. Note-se que nenhum dos dois protocolos de bombeamento precisa de um viés de dreno-fonte para executar transferências de carga. Assim, os eléctrodos de fonte e de dreno está ligado à terra durante a operação da bomba. A Figura 6 mostra a característica corrente planaltos em múltiplos inteiros de EF obtidos através da aplicação de uma unidade de dois sinal sinusoidal com a barreira de entrada (BL) e o êmbolo (PL) portão. Estes dados são levados a uma frequência relativamente baixa de condução (10 MHz) para o qual o t uning dos parâmetros pode ser realizado rapidamente. Na prática, é conveniente para operar a bomba em várias centenas de MHz, requerendo tipicamente um parâmetro de optimização 13 muito mais fina.

Figura 1. Microfabrication. (A) Ilustração esquemática dos principais passos na microfabricação. Cartoons não estão em escala. (B) Realização de uma região dopada para contatos ôhmicas. (C) Realização de óxido de porta. (D) Metalização de contatos ôhmicas. (E) microscópica imagem de um campo individual num chip após o processo de microfabricação é concluída. Tamanho do campo é de 1,2 x 1,2 mm2. Por favor clique aqui para ver uma versão maior desta figura.

Figura 2. Nanofabricação (A) processo de fabricação. Por camadas de porta individuais. Cartoons não estão em escala. (B) A nanoestrutura portão 3-camada utilizada para experiências de carga de bombagem. Esquerda: imagem SEM de um dispositivo semelhante ao utilizado para as medições. À direita:. Vistas em corte esquemático do dispositivo através de X e Y-cut-cut Clique aqui para ver uma versão maior desta figura.

Figura 3. As ligações elétricas da amostra. (A) Layout da placa de circuito impresso. (B) Ampliação de uma região do PCB com um viés-T (à esquerda) umad circuito equivalente (à direita). (C) Um chip com seis campos individuais colados no suporte do chip e fios de ligação para a ligação eléctrica com o PCB. (D) Imagem microscópica de um campo individual depois de nanofabricação. Imagem (E) SEM do layout portão no centro da região de óxido de porta. Por favor clique aqui para ver uma versão maior desta figura.

Figura 4. Testes preliminares. (A) Corrente Fonte de dreno-ac (root mean square) em função de diferentes tensões de porta. Traços são medidos com um amplificador lock-in com 50 mV RMS excitação a 113,17 Hz. Para tensão da porta indivíduo traça as tensões de porta restantes são fixados em 2,0 V, com exceção de C1 = V <em> V C2 = 0,0 V. (B) Mapa de cor de atual fonte-dreno como uma função da tensão da porta êmbolo e fonte-dreno viés de tensão. V SL = 1,5 V, V DL = 1,15 V, V BL = 0,78 V, V BR = 0,85 V, V C1 = V C2 = 0,0 V. Por favor clique aqui para ver uma versão maior desta figura.

Linhas Figura 5. Esquema da medição set-up. Vinte dc (verde) e três linhas coaxiais de RF (preto) conectar o sistema eletrônico RT para o PCB. A drenagem da bomba (roxo) está ligado a um amplificador de transimpedância e um multímetro digital através de uma optoisolador, enquanto a fonte de contacto (vermelho) está ligado à terra. Ligações à terra separadas (indicated com símbolos diferentes) são usados para a instrumentação eletrônica e as linhas elétricas criostáticas. Por favor clique aqui para ver uma versão maior desta figura.

Figura 6. quantização corrente. Pumped corrente em função de V PL para dois sinal de unidade senoidal em f = 10 MHz aplicado a portas BL e PL. Diferença de fase = 49 °, V = V PL RF RF BL = 0,31 V pp. A posição ideal do plateaux bombeamento em múltiplos inteiros de ef são mostradas como linhas horizontais vermelhas. Por favor clique aqui para ver uma versão maior desta figura.

Discussion

O protocolo descrito neste artigo descreve as técnicas para fabricar silício MOS QDs, bem como os procedimentos experimentais para testar a sua integridade funcional e operá-los como bombas-elétron único. Notavelmente, adaptando a concepção portão, o mesmo processo de fabricação pode ser utilizado para produzir dispositivos adequados para a leitura de bit quântico e de controlo 17, assim como a taxa de bombagem 12,13. Fazemos notar que muitos dos parâmetros de processo referidas neste artigo podem variar dependendo das ferramentas de fabricação usados (calibração, marca ou modelo), bem como com o tipo de substrato de silício (espessura e densidade fundo dopagem). As quantidades de dose, tais como a exposição ou tempo de desenvolvimento de litografia, gravura ou a duração da oxidação, têm de ser cuidadosamente calibrada e testados para assegurar um rendimento de confiança. Além disso, é essencial para evitar a contaminação cruzada resultantes da utilização das mesmas ferramentas de fabricação para os diferentes processos. Para este fim, um número de Critical etapas são realizadas com equipamento dedicado exclusivamente ao processamento de silício, como evaporadores de metal, fornos de oxigênio e banhos de HF.

Mais geralmente, o silício é um desenho interesse crescente como o material de escolha para realizar bombas de carga 18-20. Isto é em parte devido à perspectiva atraente de implementação de um novo padrão de corrente elétrica à base de quantum usando um processo de silício compatível-indústria. Isso beneficiaria a partir de técnicas de integração bem estabelecidos e confiáveis para escalabilidade, paralelização e sobrecarga de condução. Importante, uma tecnologia complementar completa MOS (CMOS), isento de metal tradicional como o material da porta, mostrou muito reduzidos fundo flutuações de carga em dispositivos de elétrons único 21. Tais flutuações podem ser prejudiciais em conseguir precisões metrológicos.

O protocolo discutidos aqui se limita à realização de MOS nano-dispositivos com portas de metal. Portanto, a Achieve compatibilidade industrial total e reduzir as flutuações de débito, que seria necessário para modificar as técnicas de deposição de porta e utilizar silício policristalino altamente dopado como o material da porta.

Em conclusão, as bombas MOS QD discutidos aqui recentemente combinado a vantagem tecnológica do silício com desempenho muito bom em termos de geração atual precisas 13. Isso decorre da alta flexibilidade do processo de projeto e fabricação que permitem empilhar várias camadas portão que dá para um sistema compacto e versátil. A capacidade de afinação fina resultante do confinamento electrostático do ponto juntamente com o potencial para reduzir o fundo flutuações de carga define o palco para ultrapassar os principais desafios observados noutros semicondutor bombas 22,23.

Disclosures

Os autores não têm nada a revelar.

Acknowledgments

Agradecemos KY Tan, P. Ver e GC Tettamanzi para discussões úteis. Reconhecemos o apoio financeiro do Conselho Australiano de Investigação (Grant No. DP120104710), a Academia da Finlândia (Grant No. 251748, 135794, 272806) e apoio da instalação de fabricação nacional australiana para fabricação de dispositivos. AR reconhece o apoio financeiro do regime de Pesquisador Grant University of New South Wales Início de Carreira. O fornecimento de equipamentos e suporte técnico por Universidade Aalto em Micronova Nanofabricação Centre também é reconhecido.

Materials

| Name | Company | Catalog Number | Comments |

| Silicon wafers | TOPSIL | 4 inch | |

| Electron-beam lithography machine | Raith gmbh | Raith 150two | |

| E-beam resist | MicroChem gmbh | PMMA | |

| Photoresist | MicroChem gmbh | nLOF2020 | |

| Mask aligner | Quintel | Q6000 | |

| Photoresist developer | MicroChem gmbh | AZ826MIF |

References

- Sze, S. M. Physics of Semiconductor Devices. , Wiley. Interscience, NY. 505-566 (1969).

- Moore, G. E. Cramming More Components onto Integrated Circuits. Electronics. 38, 114-117 (1965).

- Voisin, B., et al. Few-Electron Edge-State Quantum Dots in a Silicon Nanowire Field-Effect Transistor. Nano Lett. 14 (4), 2094-2098 (2014).

- Asenov, A., Brown, A. R., Davies, J. H., Savas, K., Slavcheva, G. Simulation of Instrinsic Parameter Fluctuations in Decananometer and Nanometer-Scale MOSFETs. IEEE Trans Electron Devices. 50 (9), 1837-1852 (2003).

- Zwanenburg, F. A., et al. Silicon Quantum Electronics. Rev. Mod. Phys. 85 (3), 961-1019 (2013).

- Ladd, T. D., et al. Quantum computers. Nature. 464 (7285), 45-53 (2010).

- Piquemal, F. Genevès, G. for a direct realization of the quantum metrological triangle. Metrologia. 37 (3), 207-211 (2000).

- Angus, S. J., Ferguson, A. J., Dzurak, A. S., Clark, R. G. Gate-Defined Quantum Dots in Intrinsic Silicon. Nano Lett. 7 (7), 2051-2055 (2007).

- Gonzalez-Zalba, M. F., Heiss, D., Podd, G., Ferguson, A. J. Tunable aluminium-gated single electron transistor on a doped silicon-on-insulator etched nanowire. Appl. Phys. Lett. 101 (10), 103504-103501 (2014).

- Lim, W. H., et al. Observation of the single-electron regime in a highly tunable silicon quantum dot. Appl. Phys. Lett. 95 (24), 242102-242103 (2009).

- Yang, C. H., et al. Spin-valley lifetimes in silicon quantum dots with tunable valley splitting. Nat. Commun. 4 (2069), (2013).

- Chan, K. W., et al. Single-electron shuttle based on a silicon quantum dot. Appl. Phys. Lett. 98 (21), 212103-212101 (2011).

- Rossi, A., et al. An accurate single-electron pump based on a highly tunable silicon quantum dot. Nano Lett. 14 (6), 3405-3411 (2014).

- Pekola, J. P., et al. Single-electron current sources: Toward a refined definition of the ampere. Rev. Mod. Phys. 85 (4), 1421-1472 (2013).

- Giblin, S. P., et al. Towards a quantum representation of the ampere using single electron pumps. Nat. Commun. 3, 930 (2012).

- Kouwenhoven, L. P., Austing, D. G., Tarucha, S. Few-electron quantum dots. Rep. Prog. Phys. 64 (6), 701-736 (2001).

- Veldhorst, M., et al. An addressable quantum dot qubit with fault-tolerant control fidelity. Nat. Nanotech. 9 (12), 981-985 (2014).

- Fujiwara, A., Nishiguchi, K., Ono, Y. Nanoampere charge pump by single-electron ratchet using silicon nanowire metal-oxide-semiconductor field-effect transistor. Appl. Phys. Lett. 92 (4), 042102-1-042102-3 (2008).

- Jehl, X., et al. Hybrid Metal-Semiconductor Electron Pump for Quantum Metrology. Phys. Rev. X. 3 (2), 021012-1-021012-7 (2013).

- Tettamanzi, G. C., Wacquez, R., Rogge, S. Charge pumping through a single donor atom. New J. Phys. 16 (6), 063036-1-063036-17 (2014).

- Koppinen, P. J., Stewart, M. D., Zimmerman, N. M. Fabrication and Electrical Characterization of Fully CMOS-Compatible Si Single-Electron Devices. IEEE Trans Electron Devices. 60 (1), 78-83 (2013).

- Fletcher, J. D., et al. Stabilization of single-electron pumps by high magnetic fields. Phys. Rev. B. 86 (15), 155311-1-155311-6 (2012).

- Kataoka, M., et al. Tunable Nonadiabatic Excitation in a Single-Electron Quantum Dot. Phys. Rev. Lett. 106 (12), 126801-1-126801-4 (2011).